# SEQUENTIAL CODELET MODEL A SUPERCODELET PROGRAM EXECUTION MODEL AND ARCHITECTURE

by

Jose M Monsalve Diaz

A dissertation submitted to the Faculty of the University of Delaware in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Winter 2021

© 2021 Jose M Monsalve Diaz All Rights Reserved

# SEQUENTIAL CODELET MODEL A SUPERCODELET PROGRAM EXECUTION MODEL AND ARCHITECTURE

by

Jose M Monsalve Diaz

Approved: \_

Jamie D. Phillips, Ph.D. Chair of the Department of Electrical and Computer Engineering

Approved: \_

Levi T. Thompson, Ph.D. Dean of the College of Engineering

Approved: \_

Louis F. Rossi, Ph.D. Vice Provost for Graduate and Professional Education and Dean of the Graduate College Approved: \_\_\_\_\_

Guang R. Gao, Professor Emeritus

Professor in charge of dissertation on behalf of the Advisory Committee

I certify that I have read this dissertation and that in my opinion it meets the academic and professional standard required by the University as a dissertation for the degree of Doctor of Philosophy.

Signed: \_

Rudolf Eigenmann, Ph.D. Professor in charge of dissertation

I certify that I have read this dissertation and that in my opinion it meets the academic and professional standard required by the University as a dissertation for the degree of Doctor of Philosophy.

Signed: \_\_\_\_

Xiaomin Li, Ph.D. Professor in charge of dissertation

I certify that I have read this dissertation and that in my opinion it meets the academic and professional standard required by the University as a dissertation for the degree of Doctor of Philosophy.

Signed: \_

Sunita Chandrasekaran, Ph.D. Member of dissertation committee I certify that I have read this dissertation and that in my opinion it meets the academic and professional standard required by the University as a dissertation for the degree of Doctor of Philosophy.

Signed: \_\_\_\_\_

Kalyan Kumaran, Ph.D. Member of dissertation committee

### ACKNOWLEDGEMENTS

This work is the result of several years at the CAPSL research group, under the supervision of Professor Guang R. Gao. I joined CAPSL in 2013 as an intern, and I never imagined I would stay for this long. Yet, I enjoy every single moment of my Graduate School. Professor Gao has been an inspiration. His work and ambitions, as well as his many hours of insightful conversations were crucial for the creation of this thesis. I also would like to acknowledge the patience and help from other senior CAPSL students through my PhD. In particular, Elkin García, Aaron Landwehr, Kelly Livingston, Joshua Suetterlein, Jaime Arteaga, Pouya Fotouhi, and Sid Raskar. As well as former postdoc Stephane Zuckerman, who I admire deeply, and who has been essential to the CAPSL group even to this day. Additionally, all the new students that I have been collaborating in the past three years. Ryan Kabrick, who brought two amazing students with him, Dawson Fox and Matthew Matusek; and Diego Roa, my old friend who also helped me craft the Matrix Multiplication example presented in this work.

I would also like to acknowledge Professor Sunita Chandrasekaran, one of the best professors I have met. The professionalism and dedication to her students are an inspiration. It is an honor having work with her for the past few years. Her personal and academic advise help me dealt with many difficult moments.

The University of Delaware, and in particular, the Electrical and Computer Engineering Department has supported me in many different ways. While it is difficult to mention everyone by name, I feel obliged to recognize Professor Kenneth Barner, Cynthia McLaughlin, and Gwen Looby, who bore all my crazy administrative questions and ideas. Bryan Youse, and Andrew Roosen, two excellent bosses during my ECE staff days. Amber Spivey, and Wendy Scott, who were always nice, greet me with a smile and help me out whenever I needed it. Additionally, I must acknowledge all my other professors in the department, specially Xiaoming Li, Chengmo Yang, Rudolf Eigenmann, and Andy Novicin. I have learned a great deal from each of you. Likewise, other offices in the University such as the Office of International Students and the Office of Graduate and Professional Education. In particular, Dr. Mary Martin who supported me and helped me graduate twice.

The past couple of years at Argonne National Laboratory have also played an important role in this thesis. I would like to acknowledge Kevin Harm's active participation in this project. He listened to me, and always asked the right questions. Dr. Kalyan Kumaran who also provided valuable input and supervision.

Finally, and most importantly, I must acknowledge my Family. My parents and my brother who have always given everything for my education and my future. They will always be an inspiration of hard work, dedication and love. Also, my wife, Luisa, who has brought me joy and support for many years, and specially in the past year when working on this thesis. Thanks for being there in every up and down.

I gratefully acknowledge the computing resources provided and operated by the Joint Laboratory for System Evaluation (JLSE) at Argonne National Laboratory. Additionally, this research used resources of the Argonne Leadership Computing Facility, which is a DOE Office of Science User Facility supported under Contract DE-AC02-06CH11357. This work is also supported by the National Science Foundation, under award SHF-1763654, as well as other CAPSL grants.

## TABLE OF CONTENTS

| LI<br>LI | ST C                                      | OF FIC<br>OF LIS                            | BLES                                                       | xii<br>xiii<br>xviii<br>xx             |

|----------|-------------------------------------------|---------------------------------------------|------------------------------------------------------------|----------------------------------------|

| C        | hapte                                     | er                                          |                                                            |                                        |

| 1        | INT                                       | ROD                                         | UCTION                                                     | 1                                      |

|          | 1.1                                       | The p                                       | roblem with trending parallelism                           | 4                                      |

|          |                                           | 1.1.1                                       | The evolution                                              | 5                                      |

|          | $\begin{array}{c} 1.2 \\ 1.3 \end{array}$ | -                                           | roblem                                                     | $\begin{array}{c} 10\\ 14 \end{array}$ |

| <b>2</b> | BA                                        | CKGR                                        | OUND                                                       | 16                                     |

|          | 2.1                                       | Found                                       | lation                                                     | 16                                     |

|          |                                           | $2.1.1 \\ 2.1.2 \\ 2.1.3 \\ 2.1.4 \\ 2.1.5$ | The Universal Turing Machine                               | 16<br>27<br>30<br>34<br>37             |

|          |                                           |                                             | 2.1.5.1Instruction Level Parallelism                       | $38 \\ 42$                             |

|          |                                           | 2.1.6                                       | Instruction Set Architectures and Program Execution Models | 44                                     |

|          | 2.2                                       | The C                                       | Codelet Model of Computation                               | 47                                     |

| 3        | OB                                                      | JECTI                            | IVES AND PROBLEM FORMULATION                                                    | 52                   |

|----------|---------------------------------------------------------|----------------------------------|---------------------------------------------------------------------------------|----------------------|

|          | $3.1 \\ 3.2$                                            | •                                | tives                                                                           | 52<br>53             |

| 4        | $\mathbf{TH}$                                           | E SEQ                            | UENTIAL CODELET MODEL                                                           | 55                   |

|          | $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \end{array}$ | Hieran<br>Hieran                 | ation example                                                                   | 56<br>59<br>62<br>65 |

|          |                                                         | $4.4.1 \\ 4.4.2$                 | The SCM Abstract Machine                                                        | 65<br>67             |

|          |                                                         |                                  | 4.4.2.1Tasking model                                                            | 67<br>69<br>70       |

|          |                                                         | 4.4.3                            | Programming model                                                               | 71                   |

|          | 4.5                                                     | Codel                            | et Level Parallelism: Parallelism and performance                               | 72                   |

|          |                                                         | $4.5.1 \\ 4.5.2$                 | Codelet Level Parallelism                                                       | 72                   |

|          |                                                         | 4 5 9                            | Abstract Machine                                                                | 74                   |

|          |                                                         | 4.5.3                            | Compiler techniques                                                             | 75                   |

| <b>5</b> | $\mathbf{TH}$                                           | E SUF                            | PERCODELET ARCHITECTURE                                                         | 77                   |

|          | 5.1                                                     | The A                            | architecture organization                                                       | 77                   |

|          |                                                         | 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4 | Scheduling units       Computation Units       Memory Units       Register File | 79<br>79<br>80<br>81 |

|          | 5.2                                                     | Progra                           | amming model                                                                    | 81                   |

|          |                                                         | $5.2.1 \\ 5.2.2$                 | SuperCodelet ISA                                                                | 82<br>83             |

|   |               | 5.2.3   | An example program                                                                                                                                                       | 35 |

|---|---------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 6 |               |         | TE. AN EMULATION RUNTIME FOR THE                                                                                                                                         |    |

|   | SEC           | QUEN    | TIAL CODELET MODEL    8                                                                                                                                                  | 88 |

|   | 6.1           | SCMU    | Ulate software design                                                                                                                                                    | 39 |

|   |               | 6.1.1   | The role of OpenMP                                                                                                                                                       | 39 |

|   |               | 6.1.2   |                                                                                                                                                                          | 91 |

|   |               | 6.1.3   | The SCM Machine emulation                                                                                                                                                | 93 |

|   |               |         | 6.1.3.1 Instructions and Instruction Memory                                                                                                                              | 93 |

|   |               |         | 6.1.3.2 Fetch, decode and execute $\ldots \ldots \ldots$ | 95 |

|   |               |         | 0                                                                                                                                                                        | 97 |

|   |               |         | 6.1.3.4 Codelet Level Parallelism                                                                                                                                        | 99 |

|   |               |         | 6.1.3.4.1 Sequential execution mode:                                                                                                                                     | 99 |

|   |               |         | $6.1.3.4.2$ Superscalar execution mode: $\ldots$ $\ldots$ $10$                                                                                                           | )0 |

|   |               |         | 6.1.3.4.3 Out of Order (OoO) execution mode: $\therefore$ 10                                                                                                             | )1 |

|   |               | 6.1.4   | Configuration and common structures                                                                                                                                      | )3 |

|   |               | 6.1.5   | The Codelet Class 10                                                                                                                                                     | )4 |

|   | 6.2           | Progra  | amming API and the assembly Codelet program                                                                                                                              | )6 |

|   |               | 6.2.1   | Codelets definition                                                                                                                                                      | )6 |

|   |               | 6.2.2   | Example of a print Codelet                                                                                                                                               | )8 |

|   |               | 6.2.3   | The assembly Codelet Program ISA                                                                                                                                         | 10 |

|   |               | 6.2.4   | Running the emulator                                                                                                                                                     | 1  |

|   | 6.3           | Runti   | me and Codelet Level Parallelism                                                                                                                                         | 13 |

|   | 6.4           | Profili | ing execution code 11                                                                                                                                                    | 15 |

| 7 | $\mathbf{EV}$ | ALUA'   | TION                                                                                                                                                                     | .9 |

|   | 7.1           | Evalu   | ation methodology 11                                                                                                                                                     | 19 |

|   | 7.2           | Testbe  | ed                                                                                                                                                                       | 20 |

| 7.3 | Seque          | ntial Codelet Abstract Machine mapping                                    | 122          |

|-----|----------------|---------------------------------------------------------------------------|--------------|

|     | 7.3.1          | Register File:                                                            | 123          |

| 7.4 | Exam           | ple 1: Vector Addition                                                    | 123          |

|     | 7.4.1          | Vector Addition results                                                   | 130          |

|     |                | 7.4.1.1 Manually applying optimization techniques: Loop                   | 190          |

|     |                |                                                                           | 132          |

|     |                | 1                                                                         | 132          |

|     |                | 1                                                                         | 134          |

|     |                |                                                                           | 136          |

|     |                | 7.4.1.5 Comparison between execution modes                                | 137          |

|     | 7.4.2          | Analysing the Vector Addition example                                     | 141          |

|     |                | 7.4.2.1 Evaluation drawbacks                                              | 142          |

|     |                |                                                                           | 144          |

| 7.5 | Exam           | ple 2: Dense Matrix Multiplication                                        | 146          |

|     | 7.5.1          | Three different implementations                                           | 151          |

|     | 7.5.2          | -                                                                         | 151 $154$    |

|     | 7.5.2<br>7.5.3 |                                                                           | $154 \\ 155$ |

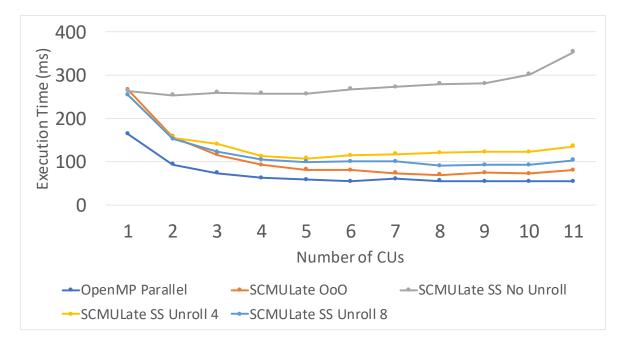

|     |                | 7.5.3.1 Execution Time                                                    | 156          |

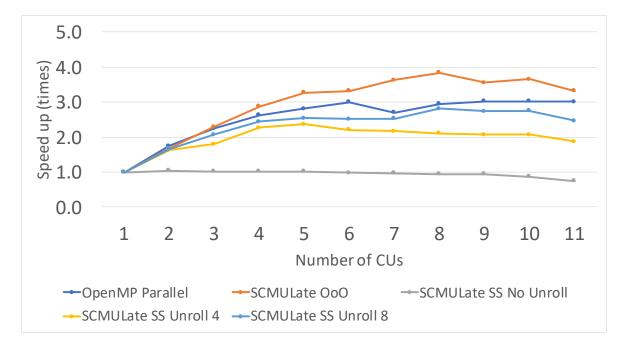

|     |                |                                                                           | 158          |

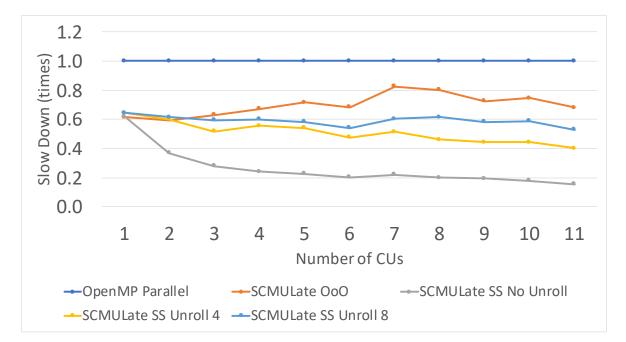

|     |                | •                                                                         | 160          |

|     |                |                                                                           | 100          |

|     | 7.5.4          | Matrix Multiplication GPU Results                                         | 160          |

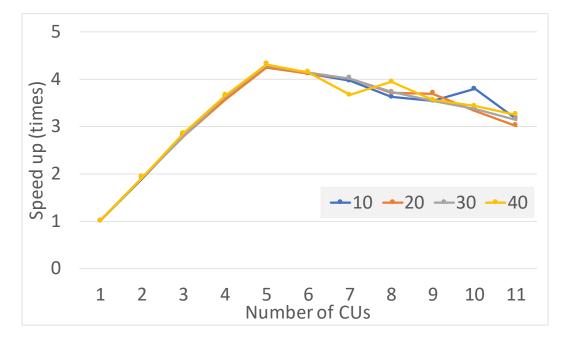

|     |                | 7.5.4.1 Execution time                                                    | 161          |

|     |                | 7.5.4.2 Scalability $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 162          |

|     |                | 7.5.4.3 Instruction size                                                  | 162          |

|     | 7.5.5          | Comparison and analysis                                                   | 164          |

| 7.6 | Defini         | ing the appropriate size of Codelets                                      | 167          |

|     | 7.6.1          | Empirical observations from Matrix Multiplication                         | 169          |

|     | 7.6.2          |                                                                           | 169          |

|     | 7.6.3          |                                                                           | 170          |

|     |                |                                                                           |              |

| 8            | REI  | LATED WORK                                      | 172 |

|--------------|------|-------------------------------------------------|-----|

|              | 8.1  | Dataflow systems                                | 173 |

|              | 8.2  | Out of Order Execution and other ILP techniques | 175 |

|              | 8.3  | Other parallel architectures                    | 176 |

|              | 8.4  | Von-Neuman/Dataflow hybrid systems              | 178 |

|              | 8.5  | Software approaches and other efforts           | 179 |

| 9            | FU   | TURE WORK                                       | 181 |

| 10           | CO   | NCLUSIONS                                       | 184 |

| BI           | BLI  | OGRAPHY                                         | 187 |

| Aŗ           | open | dix                                             |     |

| $\mathbf{A}$ | CO   | MPLETE MATRIX MULTIPLICATION CODE               | 198 |

## LIST OF TABLES

| 5.1 | tab:instSuperCodelet                                                                                                                         | 83  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.1 | List of SCMUlate supported instructions                                                                                                      | 110 |

| 7.1 | Baseline execution time for the 3 most important instructions in Vector Addition, as seen in different execution modes when running with 1CU | 142 |

## LIST OF FIGURES

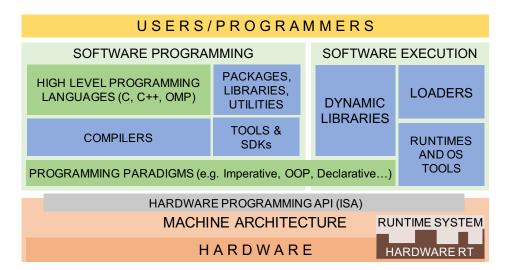

| 1.1  | Conceptual view of computer system infrastructure nowadays $\ . \ .$                                                                                                                                                                                                         | 5  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

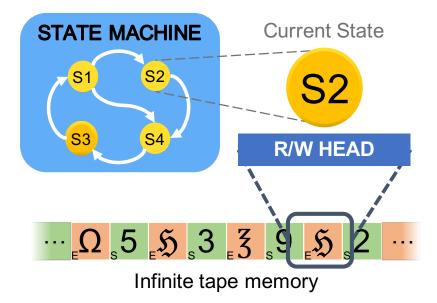

| 2.1  | Turing Machine. There are four different states $S_1$ through $S_4$ . The tape shows the two different type of Squares: E and S                                                                                                                                              | 18 |

| 2.2  | Example of an ${\tt m-configuration}$ table of the Turing Machine $\ . \ .$                                                                                                                                                                                                  | 19 |

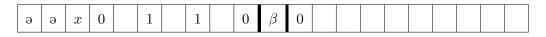

| 2.3  | Example of the ${\tt m-configuration}$ table of a ${\tt copy}$ Turing Machine .                                                                                                                                                                                              | 20 |

| 2.4  | Using skeleton Tables for representing <i>copy</i> 0 and <i>copy</i> 1 m-configurations into a single table                                                                                                                                                                  | 23 |

| 2.5  | Using skeleton Tables for representing the <i>copy</i> m-configuration table allowing different <i>following</i> states                                                                                                                                                      | 23 |

| 2.6  | Using skeleton Tables to re-write example 2.3                                                                                                                                                                                                                                | 24 |

| 2.7  | Standard forms of states in the Turing Machine                                                                                                                                                                                                                               | 25 |

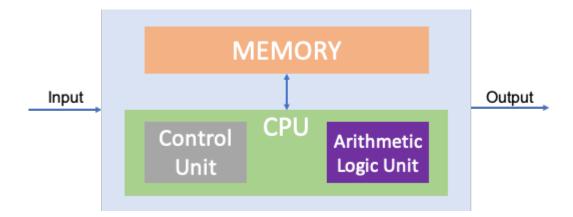

| 2.8  | Von Neuman Machine Architecture                                                                                                                                                                                                                                              | 28 |

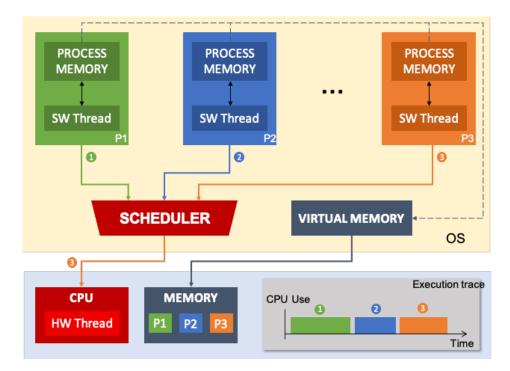

| 2.9  | Role of the Operating System in concurrency: Each process is a virtual Von Neumann machine. The OS maps each process memory to physical memory through the use of virtual memory. The OS Scheduler concurrently maps the SW Threads to HW threads through context switching. | 32 |

| 2.10 | Diagram of a multithreaded Von Neumann machine                                                                                                                                                                                                                               | 33 |

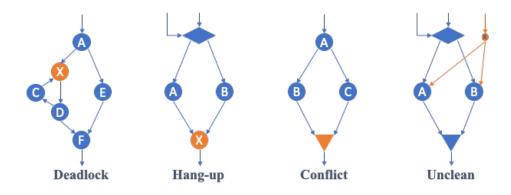

| 2.11 | Example of non well-behaved graphs ("sick" graphs). Issues highlighted in orange.                                                                                                                                                                                            | 37 |

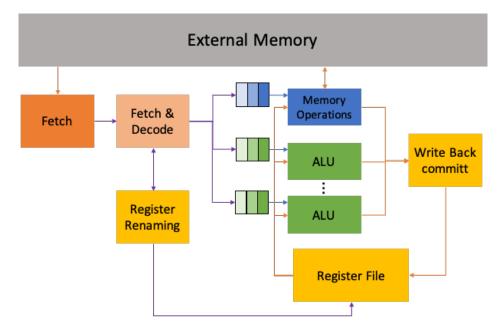

| 2.12 | Pipeline of an Out of Order architecture with Superscalar and<br>Register renaming.                                                                                                                                                                                          | 42 |

| 2.13 | Conceptual view of computer system infrastructure $\ . \ . \ . \ .$ .                                                                                                                                                                                                                                                                         | 45  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

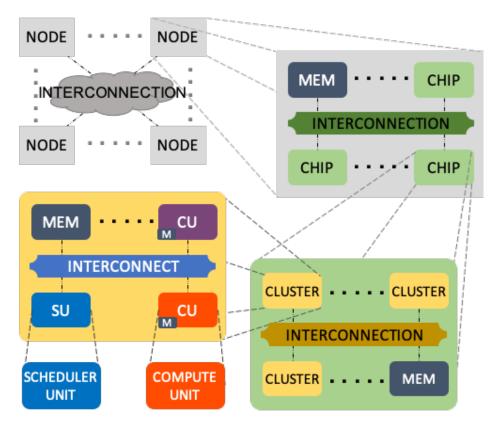

| 2.14 | Codelet Abstract Machine Depiction. Hierarchical organization of the system and its memory.                                                                                                                                                                                                                                                   | 49  |

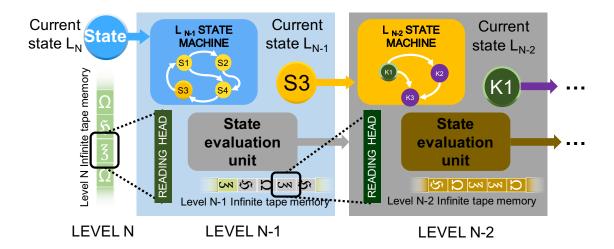

| 4.1  | A 3 levels Hierarchical Turing Machine. An state of level N is<br>expressed as an state machine of level N-1 and evaluated by level N-1.<br>Each level has an infinite memory tape used for the computation<br>performed at that level. Symbols depicted in tapes are just to<br>account for any possible symbol that is known to the machine | 60  |

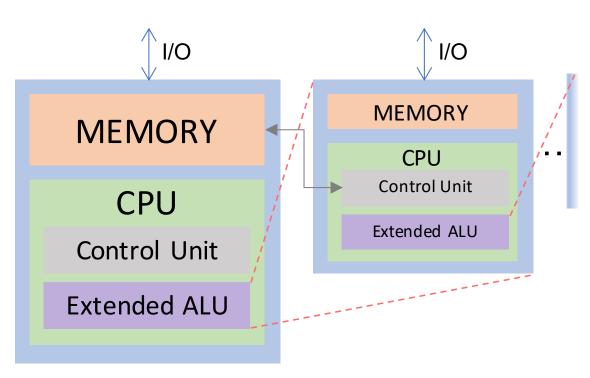

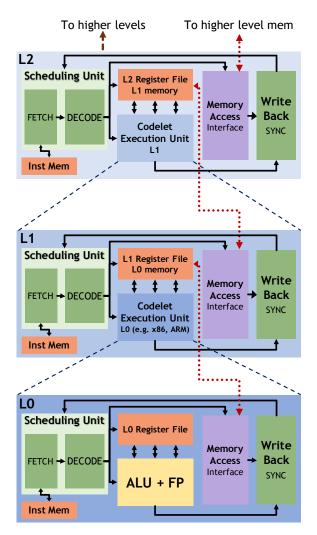

| 4.2  | Structure of the Hierarchical Von Neumann Architecture. A<br>Sequential Codelet Model Abstract machine                                                                                                                                                                                                                                        | 62  |

| 4.3  | A 3 level abstract machine of the Sequential Codelet Model that implements the Hierarchical Von Neuman Model.                                                                                                                                                                                                                                 | 65  |

| 4.4  | The Memory size to Frequency ratio of the SCM                                                                                                                                                                                                                                                                                                 | 66  |

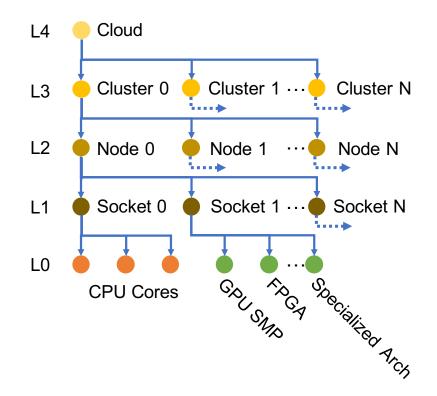

| 4.5  | Heterogeneous Sequential Codelet Model abstract machine $\ . \ . \ .$                                                                                                                                                                                                                                                                         | 75  |

| 4.6  | Extending the hierarchy beyond L2                                                                                                                                                                                                                                                                                                             | 76  |

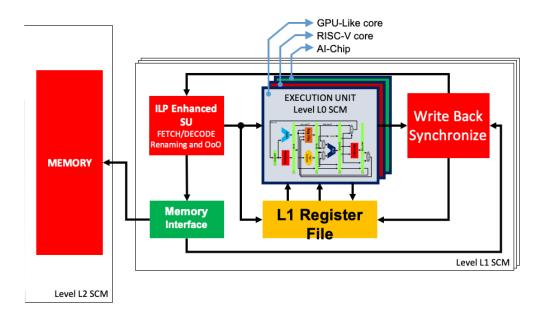

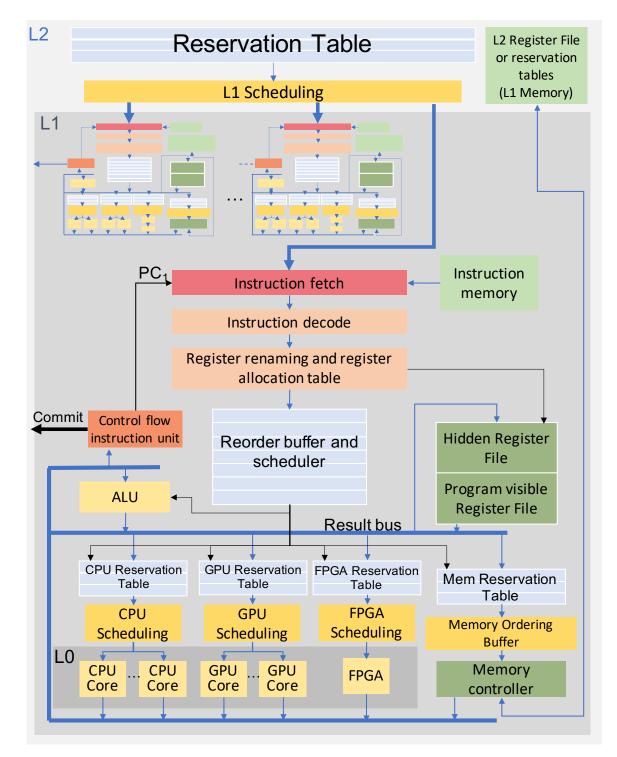

| 5.1  | Diagram of the SuperCodelet architecture                                                                                                                                                                                                                                                                                                      | 78  |

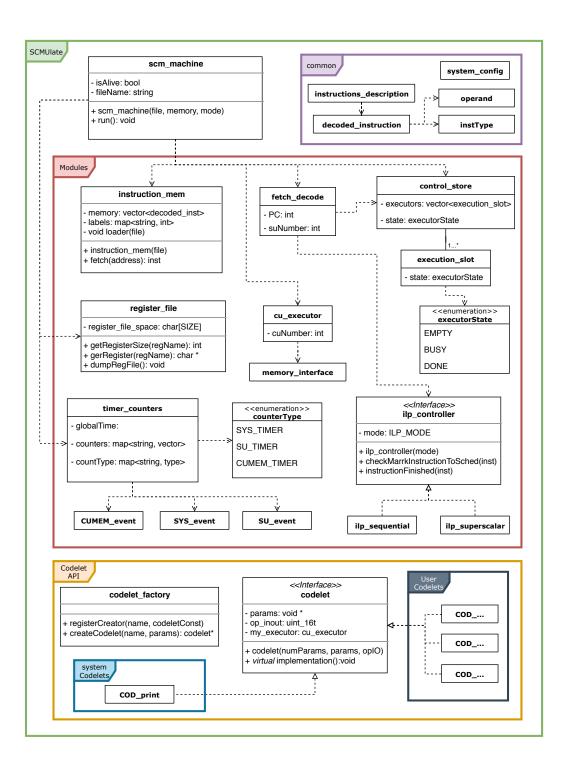

| 6.1  | SCMUlate UML Classes Diagram                                                                                                                                                                                                                                                                                                                  | 90  |

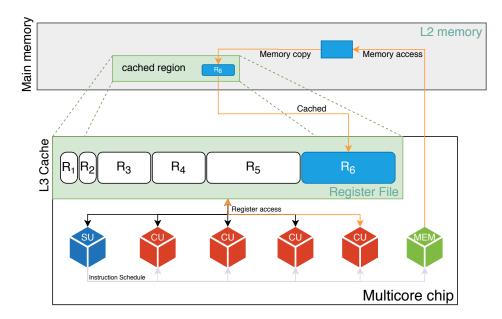

| 6.2  | Register file emulation mechanism on SCMUlate                                                                                                                                                                                                                                                                                                 | 98  |

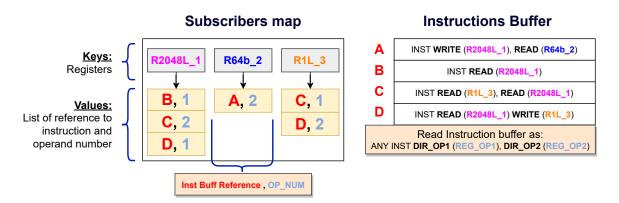

| 6.3  | Example of the content in the subscribers map with respect to the instructions in the instructions_buffer                                                                                                                                                                                                                                     | 102 |

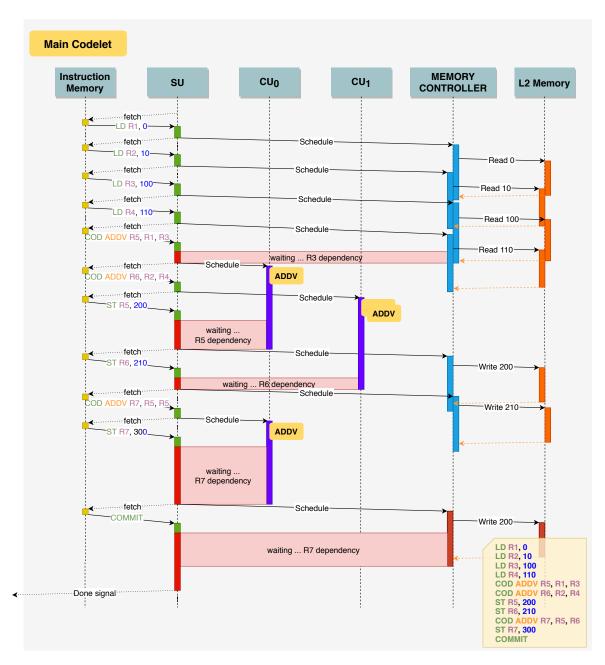

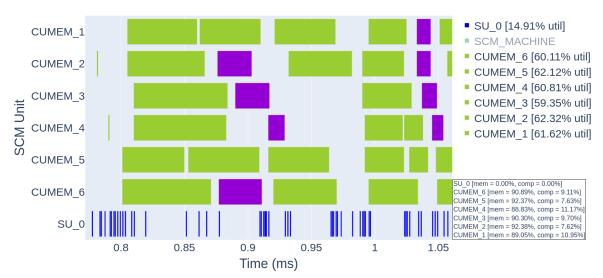

| 6.4  | Time diagram of the execution of a Codelet using a superscalar approach with 2 Compute Units. See the executing Assembly Codelet Program on the bottom right                                                                                                                                                                                  | 114 |

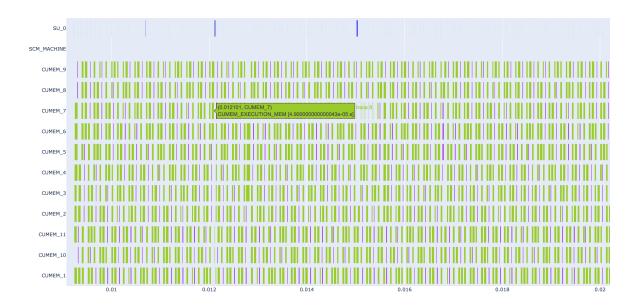

| 6.5  | Interactive trace visualization example                                                                                                                                                                                                                                                                                                       | 118 |

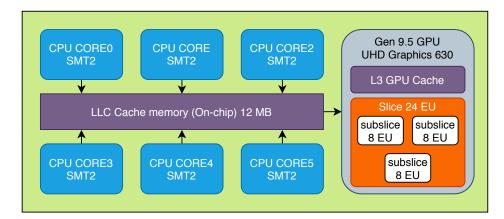

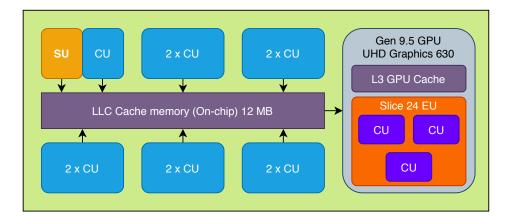

| 7.1  | Architecture block diagram of the Intel Core i7-8700K containing the Intel Gen9 integrated GPU                                                                                                                                                                                                                                                | 120 |

| 7.2  | Architecture block diagram of the Intel Core i7-8700K containing the Intel Gen9 integrated GPU                                                                                                                                                                                                                                                | 122 |

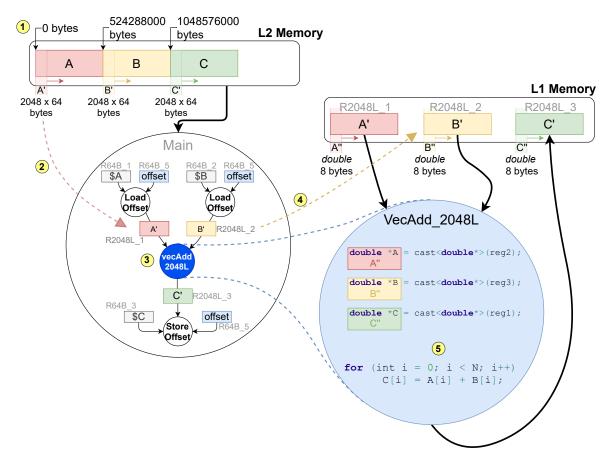

| 7.3  | Structure of memory and computation for Vector Addition using<br>SCM running on SCMUlate. 1) L2 memory contains the original 3<br>vectors (A,B,C) in a single flat memory allocation. 2) load and store<br>operations of L1 fetch part of the whole array, according to the L1<br>register sizes (e.g. 2048x64 bytes) (A', B' and C'). 3) L1 Codelets use<br>these registers to perform computation. They are evaluated at L0. 4)<br>Each register in L1 belongs to L1 memory space. Then L0<br>computation access these registers through memory operations. Each<br>read/write access as much as L0 register size (A", B" and C"). 5)<br>Actual computation performed at L0 | 124 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

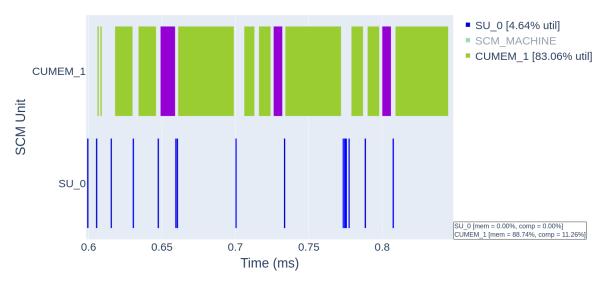

| 7.4  | Vector Addition execution trace for the sequential mode on the SCMUlate emulator. 3 loop iterations on 1 CU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 133 |

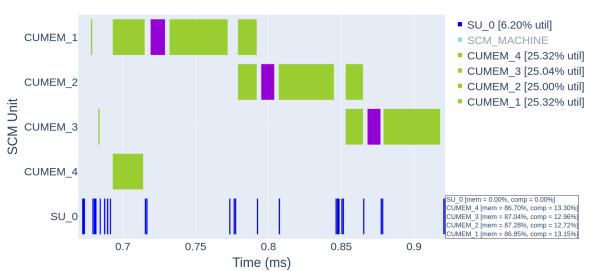

| 7.5  | Vector Addition execution trace for the Superscalar Codelet Level<br>Parallelism mode on the SCMUlate emulator. 3 Loop iterations on 4<br>CUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 134 |

| 7.6  | Vector Addition unrolled 4 times. Execution trace for the Superscalar<br>Codelet Level Parallelism mode on the SCMUlate emulator. Zooming<br>on at least 4 loop iterations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 136 |

| 7.7  | Vector Addition execution trace for the Out of Order Codelet Level<br>Parallelism mode on the SCMUlate emulator. Zooming in to the<br>initial loops.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 137 |

| 7.8  | Execution time comparison for different execution modes. Superscalar and Out of order used 5 CUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 138 |

| 7.9  | Vector Addition execution time for different number of CUs. The size of the vector is the same in all the cases. Lower is better                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 139 |

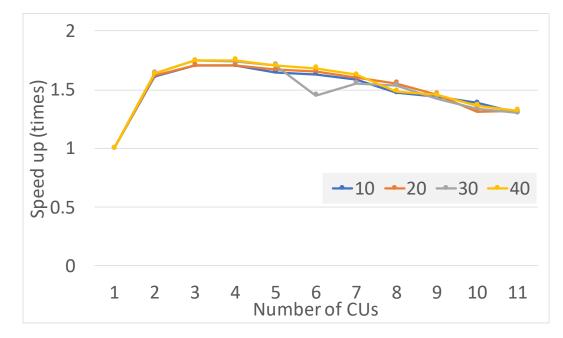

| 7.10 | Speed up progress with the number of CUs as compared against the execution with 1 thread within each mode of operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 140 |

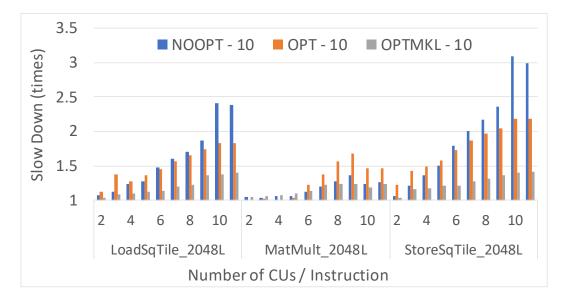

| 7.11 | Slow down in comparison to a simple baseline using OpenMP. The higher the better.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 141 |

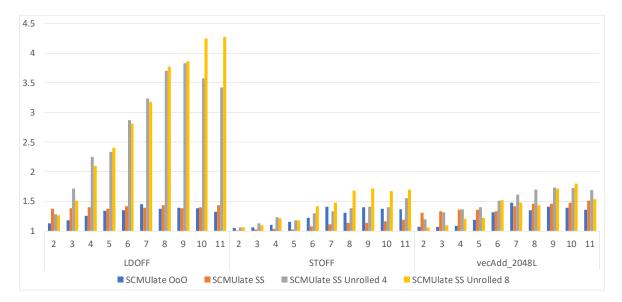

| 7.12 | Average execution time of the three most important instructions in<br>the execution of Vector Add in comparison to the number of CUs and<br>the implementation approach. Lower is better                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 143 |

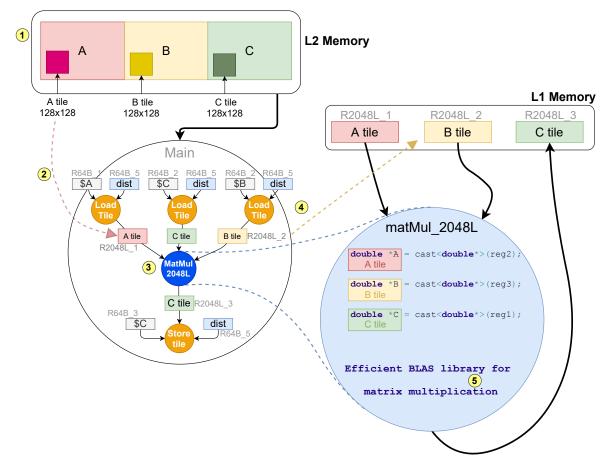

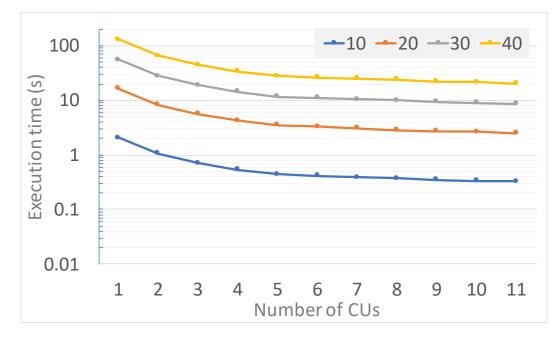

| 7.13 | Tiling strategy for matrix multiplication. 1) Matrices are divided into<br>tiles of 128x128. 2) A special memory Codelet performs a load<br>operation on tiles A, B and C. Since tiles are usually non-contiguous,<br>a distance is send as part of the operands. 3) the matrix<br>multiplication Codelet is applied. 4) the Rnum_2048R registers contain<br>the 128x128 tile. 5) Regular matrix multiplication can be applied, it<br>is possible to use highly optimized BLAS libraries | 147 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

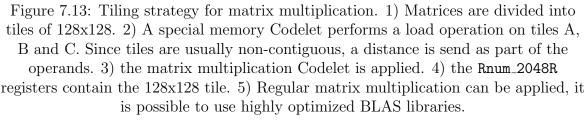

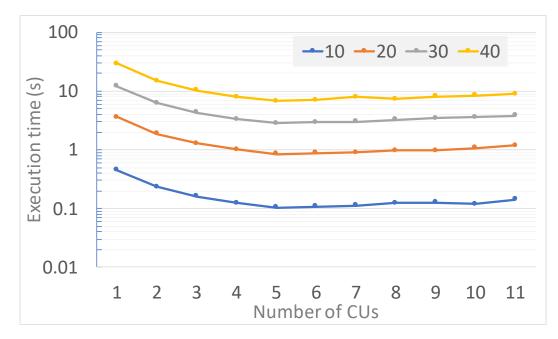

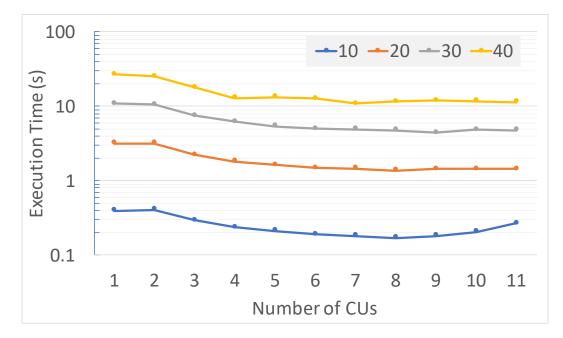

| 7.14 | Execution time vs number of CUs for the naïve version of Matrix<br>Multiplication. Logarithmic scale in the vertical axis                                                                                                                                                                                                                                                                                                                                                                | 156 |

| 7.15 | Execution time vs number of CUs for the optimized version of Matrix Multiplication. Logarithmic scale in the vertical axis.                                                                                                                                                                                                                                                                                                                                                              | 157 |

| 7.16 | Execution time vs number of CUs for the Intel MKL version of Matrix Multiplication. Logarithmic scale in the vertical axis                                                                                                                                                                                                                                                                                                                                                               | 157 |

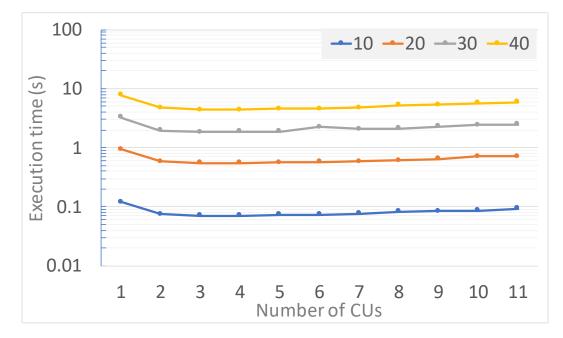

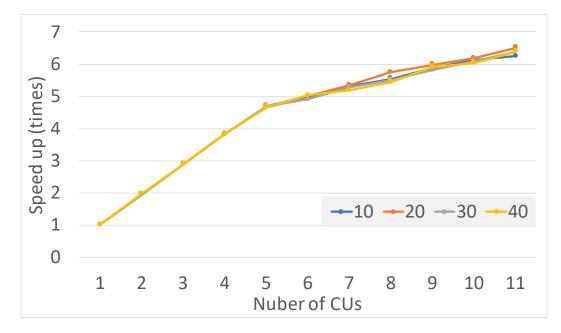

| 7.17 | Strong scaling for the naïve version of Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                            | 158 |

| 7.18 | Strong scaling for the user optimized version of Matrix Multiplication.                                                                                                                                                                                                                                                                                                                                                                                                                  | 159 |

| 7.19 | Strong scaling for the Intel MKL version of Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                        | 159 |

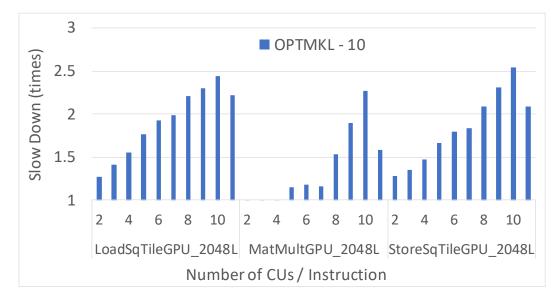

| 7.20 | Codelet Performance degradation for Matrix Multiplication.<br>M=N=K=10 tiles                                                                                                                                                                                                                                                                                                                                                                                                             | 161 |

| 7.21 | Execution time vs number of CUs for the GPU version of the Matrix Multiplication Codelet. Logarithmic scale in the vertical axis                                                                                                                                                                                                                                                                                                                                                         | 162 |

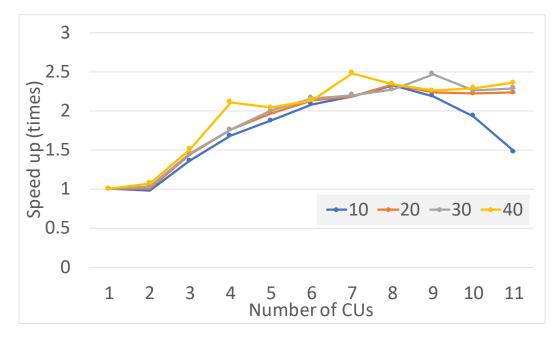

| 7.22 | Strong Scaling for the GPU version of the Matrix Multiplication<br>Codelet. Logarithmic scale in the vertical axis                                                                                                                                                                                                                                                                                                                                                                       | 163 |

| 7.23 | Strong Scaling for the GPU version of the Matrix Multiplication<br>Codelet. Logarithmic scale in the vertical axis                                                                                                                                                                                                                                                                                                                                                                       | 163 |

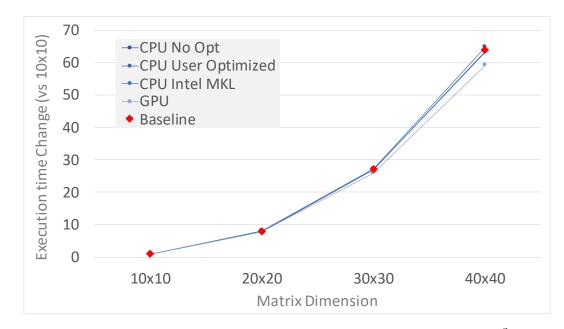

| 7.24 | Big O for Matrix Multiplication as observed from L1. $\mathcal{O}(N^3)$ for the implemented MM.                                                                                                                                                                                                                                                                                                                                                                                          | 164 |

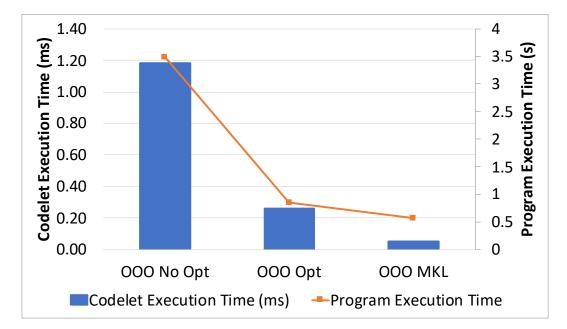

| 7.25 | 5 CUs and M=N=K=20. Bars: Codelet execution time (left axis).<br>Line: Program Execution Time (right axis).                                                                                                                                                                                                                                                                                                                                                                              | 165 |

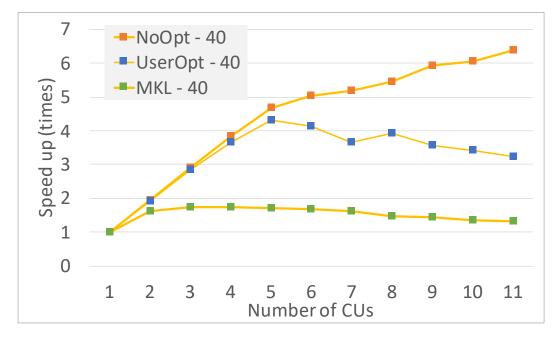

| 7.26 | M=N=K=40. Scalability comparison for different implementations                                                                                                                                                                                                                                                                                                                                                                                                                           | 167 |

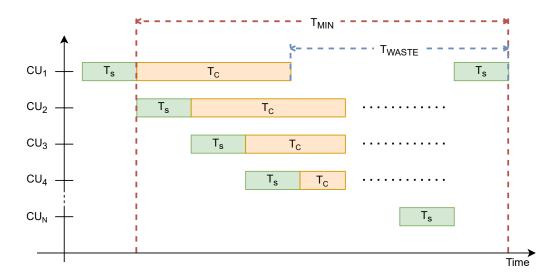

| 7.27 | Understanding Sequential bottleneck. $T_s$ Time to schedule an                                      |     |

|------|-----------------------------------------------------------------------------------------------------|-----|

|      | instruction into a CU. $T_c$ Compute time. $T_{min}$ minimum compute                                |     |

|      | time to avoid $T_{waste}$ sub-utilization $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 168 |

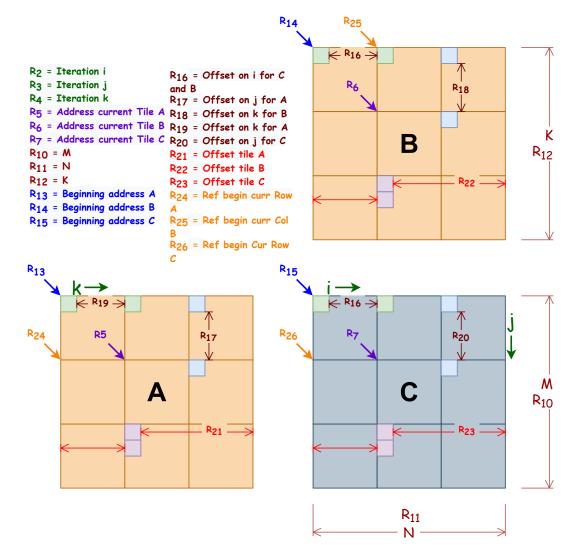

| A.1  | Guide image for Matrix Multiplication Implementation in SCM.                                        |     |

|      | Registers and their corresponding meaning                                                           | 198 |

### LIST OF LISTINGS

| 2.1 | Example code for Superscalar ILP                                                  | 39  |

|-----|-----------------------------------------------------------------------------------|-----|

| 2.2 | Example code for Register Renaming ILP                                            | 40  |

| 4.1 | Motivation Example                                                                | 58  |

| 5.1 | Main Codelet definition at level L1                                               | 86  |

| 5.2 | Sum Codelet definition at level L0                                                | 87  |

| 5.3 | Sub Codelet definition at level L0                                                | 87  |

| 6.1 | The Print Codelet implementation                                                  | 109 |

| 6.2 | Example of using the Print Codelet                                                | 110 |

| 6.3 | Use example of the SCMUlate runtime                                               | 112 |

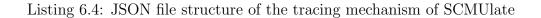

| 6.4 | JSON file structure of the tracing mechanism of SCMU<br>late $\hdots$             | 117 |

| 7.1 | Main Codelet for the Vector Addition program                                      | 126 |

| 7.2 | L0 Codelet VecAdd_2048L implementation                                            | 128 |

| 7.3 | SCMUlate program for Vector Addition. Runtime creation and Main Codelet creation. | 129 |

| 7.4 | Loop unrolling of size 4 for Vector addition. : A                                 | 131 |

| 7.5 | Matrix Multiplication 1 tile: C                                                   | 148 |

| 7.6 | Definition and implementation of the LoadSqTile_2048L Codelet                     | 150 |

| 7.7 | No optimized version of matMult_2048L                                             | 152 |

| 7.8 | User optimized version of matMult_2048L                                           | 153 |

| 7.9  | Intel MKL version of matMult_2048L                                                                           | 153 |

|------|--------------------------------------------------------------------------------------------------------------|-----|

| 7.10 | Definition of the GPU Codelet matMulGPU_2048L using Intel's MKL support for gen9 GPU and OpenMP 5.1 features | 155 |

| A.1  | L2 Memory structure for Matrix Multiplication on SCM $\ . \ . \ . \ .$                                       | 199 |

| A.2  | Matrix Multiplication NxM tiles: $C = C + A^*B$ . Constant declaration.                                      | 200 |

| A.3  | Matrix Multiplication NxM tiles: C = C + A*B. Loop j and k $\hdots$                                          | 201 |

| A.4  | Matrix Multiplication NxM tiles: C = C + A*B. Loop i $\ldots \ldots \ldots$                                  | 202 |

| A.5  | Matrix Multiplication NxM tiles: $C = C + A^*B$ . Iteration variable increments loop i                       | 203 |

| A.6  | Matrix Multiplication NxM tiles: $C = C + A^*B$ . Iteration variable increments loop k                       | 204 |

| A.7  | Matrix Multiplication NxM tiles: $C = C + A^*B$ . Iteration variable increment loop j                        | 205 |

### ABSTRACT

In sequential computers, the Instruction Set Architecture provides a clear division between software and hardware. Separation of software and hardware through a well defined contract enabled decades long of seamless evolution of computer systems. The end of Dennard's scaling and slow down of Moore's law has forced architects to abandon purely sequential architectures in favor of parallel/distributed and heterogeneous systems. The new era represents a new spring of computer architectures. However, the ISA contract has been broken. It is mandatory to reconcile the abstraction between hardware and software in order to recover performance, portability, and programmability.

Sequential architectures take advantage of Instruction level parallelism to overlap the execution of instructions. These techniques use dataflow to implicitly perform side-effect free parallel execution of code. On the other hand, parallel programming often requires explicit reasoning of workload distribution, communication, memory synchronization and worker management. This thesis proposes the Sequential Codelet Model, a program execution model for parallel, heterogeneous and distributed execution of programs. It defines a machine abstraction (namely hierarchical Von Neumann machine), that recognizes the natural hierarchical structure of computer systems. Programming of the machine uses a hierarchical imperative programming model reassembling an Instruction Set Architecture at each level. A Codelet is the name given to an "instruction" of a level, as expressed in terms of instructions of the level below. By means of Instruction Level Parallelism inspired techniques, parallel/distributed execution of programs is achieved. The final system leverages the vast progress made for sequential computers. Finally, We present a the Super Codelet Architecture, a possible realization of the Sequential Codelet Model.

## Chapter 1 INTRODUCTION

Computer systems are highly complex machines composed of a large number of parts interacting with each other. Throughout history, hardware and software have constantly evolved aiming to push the limits of what computers can do. Computer architects have competed to define high performance computing organizations with faster processing capabilities. On the other hand, software developers have design a large infrastructures that eases programming and utilization of computer systems. In general, computers are expected to deliver increased performance in every new generation, and software is expected to be easy to understand, create and extend while utilizing most of the available resources. Finally, rapid evolution requires re-usability across generations of systems, enabling a seamless evolution. These three aspects: Performance, Portability, and Programmability (or just 3P) have continuously driven computer innovation. For years, sequential computing provided a system abstraction and execution model that fostered these three properties. However, the arrival of parallelism has proven difficult to maintain them.

Following the advice of Hennessy's and Patterson's Turing Award lecture [1], we shall revisit some of the history of computer architecture. There are three major creations that lead to the sequential computing success. First, the Turing Machine introduced by Allan Turing in 1936 [2] which provided the necessary mathematical model. Second, the definition of the Von Neumann architecture in 1945 [3] that narrowed down the components of the computer system and their interaction into a specific system organization. And third, the introduction of a standardized Instruction Set Architecture as a single interface between hardware and software in the 1960's [4] by Frederick Brooks and its IBM/360 design team. The standardization of the Instruction Set Architecture (ISAs) worked as a long lasting contract between hardware and software. As long as this contract was respected, each part could independently evolve its capabilities. On one hand, hardware designers focused on improving processor's frequency of operation and scaling down feature size of transistors. Higher frequencies and more transistors meant increased throughput and complexity. Software developers, on the other hand, were relieved of the need to constantly adapt their programs to new systems. As long as both hardware and software used the same ISA and respected the architecture's execution model provided by the hardware (i.e. Turing Machine and Von Neumann model), they could evolve programming models and compilers continuously.

ISA is almost a synonym of the system's architecture. There are multiple possible implementations of the same ISA, each with different characteristics. However, given an architecture, it is possible to execute the same program in every implementation that follows exactly the same ISA (i.e. Portability). Some of the most advanced implementations that are available today parallelize and re-arrange the execution of instructions without interfering with the running software or its correct result. A parallel execution of instructions is achieved through dataflow inspired techniques in a process that is completely transparent to the user. For a subset of the instructions in the program stream, dependencies are discovered and maintained at runtime, allowing for the order of execution of instructions to be changed. Furthermore, as long as instructions are committed in the order they are described (i.e. program state changes are performed in-order), the user is not aware (and does not need to be aware) of the runtime execution order. It is still possible to increase performance for a given implementation of an ISA. An avid programmer may change their code to exploit these execution mechanisms, but even so, the developer is not required to think of the potential hazards of the parallel execution.

The end of Dennard's scaling [5] and slowing of Moore's law during the past 2 decades [1] has limited the ability to improve sequential architectures through the same mechanisms used by the industry for over 30 years. Consequently, computer architects

were forced to adopt parallelism, at first, by means of increasing the number of cores present in the same system (i.e. multicore architectures). Most recently, architects have shifted towards heterogeneous systems composed of multiple units each specialized in different computational patterns or application specific operations. Although this seems like an reasonable step, maintaining the Von Neumann abstraction over multiple cores has presented difficulties and challenges, specially when aiming to maintain the aforementioned 3P properties. We will discuss this further in the next subsection. The new architectures have revived interest in parallel computer architectures that already existed in the 70s and 80s, albeit its lack of success in the past. Nowadays, it is an accepted fact that computer systems must be parallel, heterogeneous and distributed machines.

Unlike sequential computing, trending parallel processing lacks of a broadly acceptable common abstraction that allows a division between software and hardware (similar to an ISA). Hardware evolution is usually slower than software due to its complexity. In order to utilize the newly introduced parallel hardware (i.e. multicore and heterogeneous systems) software (and developers) have been burdened with the task of creating this abstraction. Three big changes arrived to software. First, the concept of thread was introduced in the operating system. Second, programming models and languages were leveraged to explicitly express parallelism. Third, runtime systems were introduced to emulate machine abstractions and organizations. Nowadays, parallel programmers are responsible of workers creation, workers synchronization, and memory management across workers.

This thesis aims to provide a system and program organization for highly parallel, heterogeneous and distributed systems. This work intends to leverage the sequential computation abstractions (i.e. Turing Machine, Von Neumann model and Instruction set architectures) and extend it beyond the core unit. It defines a model of computation for parallel program execution that spans across the whole computer system infrastructure. The aspiration is to take advantage of the original sequential abstraction to exploit parallelism through ILP techniques, but for the execution of tasks that define more complex mathematical operations.

### 1.1 The problem with trending parallelism

The problem of parallelism, in general, is one of creation, communication and coordination of workers, tasks and resources. In addition, there are three requirements for general purpose parallel computing: 1) The program execution must use the available resources efficiently (i.e. high performance), 2) performance must be carried through multiple system generations and system architectures (i.e. performance portability), and 3) it is easy for a programmer to describe such program, reducing time-to-solution (i.e. programmability). Current trending parallelism relies on two major architectures: Shared memory multi-core systems and accelerator-based systems (e.g. GPGPUs) that use a SPMD execution model. Furthermore, there are currently two trending communication mechanisms across workers: 1) Message Passing (e.g. MPI) and Shared memory. I focus here on these four elements.

The problem with trending parallelism, in particular, is twofold. First, the lack of a common abstraction, namely Program Execution Model (PXM) as previously defined [6][7][8]. Second, current abstractions aim to maintain a Von Neumann view of the system. A PXM describes the execution of a program in a parallel system as a whole, and it should serve as a common view for hardware designers, system software developers, and programmers. A PXM allows for a single strategy to be used in order to represent and execute programs in the system. Such abstraction is similar to the role that the Universal Turing Machine, the Von Neumann model and the Instruction Set Architecture had in sequential system. All of which allowed an smooth evolution of hardware and software in sequential computer systems. The following paragraphs aim to understand the evolution of parallelism in the recent years and explain why these two problems are critical for the evolution of computer systems.

### 1.1.1 The evolution

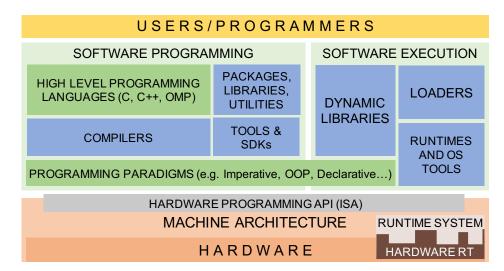

Parallelism is not a new idea in computer architectures. It dates back to the early times of computer architectures, but contrary to the early years of parallel computing, mainstream parallel systems are now easily available. Modern parallelism arrived to an already existing infrastructure (as seen in figure 1.1) that relies on general purpose computation and urges backwards compatibility. With the decay of Dennard's Scaling and slow down of Moore's law, architects needed a solution to continue growing computational power of systems. Single core performance advancements hindered, and systems started featuring multiple cores (or independent threads in the case of SMT) side by side in a single die. This approach was simple for hardware development and allowed to keep backwards compatibility with existing software infrastructure. Furthermore, it was easy for the operating system to trade concurrency for parallelism when applications were running independently.

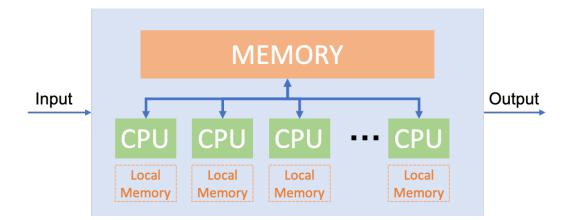

Figure 1.1: Conceptual view of computer system infrastructure nowadays

Multicore architectures are the simplest form of parallelism. They comprehend a number of computational units (namely CPUs or hardware threads) that are independently programmable workers. That is, the inner operation of a single worker does not inherently affect the operations of another worker. To coordinate execution of parallel programs in multicore systems additional communication mechanisms are necessary. Given the already existing influence of Von-Neumann architectures, memory is the preferred method of communication in multi-core systems. Cores use reads and writes to memory to share information and influence program execution of other workers. Consequently, the order of memory operations have an impact on the communication across cores, and therefore on the overall execution of programs. The most common multicore abstraction is composed of multiple homogeneous cores all connected to a monolithic memory. Although memory is often seen as a single unit, memory organizations are not monolithic. Due to performance benefits, memory is divided into different physical locations, allowing a single memory address to be potentially located in different physical locations. The most common example is cache hierarchies.

A more recent system design trend are accelerators (or co-processors) featuring specialized hardware that optimize execution of specific sections of the program for a sub set of applications. Accelerators have proven that a heterogeneous system could provide great benefits towards computational performance. Perhaps the two most common type of accelerators right now are GPGPUs, and brain-inspired neuromorphic accelerators such as Google's Tensor Processing Unit [9] or IBM's TrueNorth project [10]. The latter have shown interesting results for brain-inspired applications. Accelerators are architectures that are created to exploit performance given certain characteristics such as optimizing application specific operations, or enabling data parallelism in hardware. When a program fits the execution model of the accelerator, its performance is improved.

Systems featuring GPGPUs have been successful when it comes to data parallelism and are the current trend in the fastest supercomputers of the world according to the Top500 list [11]. These systems heavily borrow from vector machines [12] and use Single Program Multiple Data (SPMD) and Single Instruction Multiple Data (SIMD) execution models. In these models all the threads receive the same stream of instructions, but a unique identifier of the thread allows for accessing and processing different data in each thread. GPGPUs contain hundreds or even thousands of simplified cores that are relatively simpler and slower than the CPU counterparts. Cores are also grouped into set of cores that usually share memory and other resources. Multiple groups of cores are placed into the same device, and it is possible to use multiple devices. The structure of GPGPUs is a hierarchical and programs usually adapt to this hierarchy in order to utilize the whole system.

Accelerators often feature non-traditional ISAs, therefore, they rely on commodity hardware, usually referred to as the host, to start and coordinate the execution of the program. Under this model, certain segments of computation are offloaded to the accelerator, while the creation and coordination of program is left to the host.

Parallelism in software has evolved with parallelism in hardware. Prior to the arrival of mainstream parallel systems, operating systems (OS) already supported concurrency of different processes. The use of virtual memory and time-slicing scheduling techniques allows independent programs to share system resources transparent to the user. Communication between processes requires the intervention of the OS. Additionally, due to the isolation of processes, messages must make use of intermediate storage such as reserved kernel address space or I/O. Processes are software representation of the von Neumann machine, while the OS guarantees its mapping to the underlying hardware. In multi-core systems it is easy for an operating system to trade concurrency for parallelism. The independent behavior of processes maps to that of CPU cores in multicore systems. Adaptation between single-core and multi-core OS runtimes featured a parallel scheduler with restrictions on shared resources coordinated by the single kernel. In the absence of synchronization between instruction streams of different processes and their respective memory spaces, the OS is the only mediator for the communication between processes and resource sharing, reducing potential side effects to specific interactions that obey a strict sequential order.

Message passing interfaces (MPI) was created to enable explicit communication across processes, reducing the intervention of the operating system. Thanks to process isolation, MPI can easily spawn across different compute nodes by using already existing networks to distribute messages. Since memory is independent for each process, MPI requires interaction between the program's user space and the operating system's kernel space for communication. Furthermore, when spawning across nodes, this communication also involves different drivers and hardware. All these makes cooperation between processes expensive, resulting in a penalty to performance [13, 14], that must be accounted for when parallelizing software.

Multi-threading programming allows creation of multiple threads on the same process, sharing the same resources such as memory address space. Multi-threading removes the shield across processes placed by virtual memory, while at the same time reducing the operating system's role and interaction during program execution, potentially reducing overhead and providing more performance. The number of threads in a process do not have to map the number of physical cores in the system. Instead the operating system can concurrently execute threads with the means previously described. However, it has been shown that over-subscription of threads that compete for the same resources hampers performance [15], and concurrent execution of threads may leave to potential deadlocks, if not handled correctly.

Multi-threading still relies on a Von Neumann view of the system with a monolithic perspective of memory. CPU core's performance heavily relies on the use of cache-like memories (among other pre-fetching mechanisms) that reduce latency of memory access. Caches are transparent to the user and are not part of the software thread abstraction, but a given unique memory address in the thread's memory space may map to different physical locations in hardware. Shared memory systems on multi-core architectures introduce a problem: Out of all potential memory locations, and their respective values, what is (are) the correct value (values) a worker can observe at a certain moment of time? Memory models are used to determine the set of admitted values in the presence of multiple workers (observers and producers) [16].

Multi-treading requires programmers to reason about all potential side effects that could occur in memory during the execution. Order of events is critical for synchronization of workers. Relaxed memory models with large set of correct values increase potential side effects. Therefore, most of the commodity multi-core systems available nowadays have been design to respect the sequential consistency memory model [17]. Cache coherence protocols are built around the memory hierarchy to maintain the illusion of an ordered sequence of memory operations that allows a single value to be observed by every worker at a given time. Additionally, different flavors of atomic memory operations are often provided by these systems to allow for a more strict definition of the order of memory operations.

With the arrival of commodity parallel systems, it was still necessary to adapt previously existing high level programming models and programming languages to be able to support parallelism. Software threads are managed by an OS libraries and kernel functions (e.g. POSIX Threads). An application can request and manage thread resources through different calls exposed as a system library. Software and hardware threads are flexible and allow to be building blocks of more complex models. Furthermore, they enable backward compatibility with an already existing software infrastructure. Therefore, high level programming languages would only require a library or module that connects the OS API with the particular semantics of the programming language.

Consequently, mainstream programming models have been extended with semantics to express parallelism. Extensions have been proposed to define creation, communication and coordination of workers, tasks and resources. Currently there is no widely acceptable parallel programming model, and in order to take advantage of the parallel resources there is a myriad of frameworks that implement different programming models for parallelism. Multi-threading, for example, provides full flexibility, but the burden lays completely on the programmer [18]. Another example is the Fork-join models. The program starts sequentially and, at a certain point in computation a number of workers are spawned. Once they have finished executing they join into a single barrier and sequential execution resumes. Workers may have local private memory and there may be global shared memory. Depending on the implementation, communication is allowed across workers, but it must be coordinated by the programmer. Yet another example of a programming model is tasking. This model is heavily inspired by dataflow models of computation. tasks are segments of code that are executed when their dependencies are satisfied and the necessary resources are available. There are data dependencies defined as a producer-consumer relationship, and control dependencies, defined as the order in which tasks need to be executed. Tasking usually defines a graph of dependencies either at runtime or statically at compile time.

Accelerators have also been considered. Accelerators often come with low level languages that extend from already existing languages (e.g. Cuda, HIP, or SYCL). Additionally, other programming languages and frameworks (e.g. OpenMP, and OpenACC) have been extended to account for heterogeneity, allowing the user to express computation targeting the given architecture. Finally, there are libraries which provide application specific operataions which ultimately use the accelerator as part of its implementation (e.g. TPU Tensorflow, cuCNN, and Intel's MKL).

### 1.2 The problem

Sequential computing built up upon two models: The Turing Machine and the Von Neumann architecture. These models allowed a common view of the system the between hardware and software development, provided a solid ground for the evolution of computer systems. However, the introduction of parallelism has shaken these abstractions.

Multicore architectures enable backwards compatibility by using already existing ISAs in each core. However, these system struggle to maintain the 3P properties. Programmability suffers from two angles. First, independent worker creation and synchronization is tedious. Second, as memory operations affect the result of the computation, it is often necessary to enforce an order in memory operations to easily understand program behavior. Consequently, multicore systems use mechanisms to guarantee this order operations (e.g. cache coherency protocols) which ultimately degrade performance as the number of cores increases. Performance is also heavily dependent on other system's elements which are often left outside of the multi-core abstraction (e.g. cache organization, memory bandwidth, interconnect architecture, and memory access times). The lack of accountability for these concepts in the software abstractions ultimately degrade portability when these elements change from system to system.

Some accelerators have proven to improve performance by reducing the overhead, increasing the number of workers and allowing different execution models to be used. In addition to performance, programmability also improves with accelerators as they ease worker creation and coordination. However, the host-accelerator machine abstraction centers its execution into the accelerator and usually leaves behind other compute capabilities such as the host. This problem is exacerbated by the distance between host and device, leaving the host as a simple scheduler of computation. Finally, there host-accelerator machine abstraction has not been formalized to allow portability across generation of systems.

Regardless of the programming model, there needs to be a mapping in between the abstract machine of the hardware, and the abstract machine of the programming model. With the lack of a common abstraction at the hardware level, parallel programming models have been tasked to come up with abstractions on how to organize computation to take advantage of parallelism. Due to the aforementioned evolution of hardware and parallelism, most of the programming models rely on runtimes that are software implemented and linked against the OS libraries that provide thread creation and management. These implementations use hardware threads, software threads and processes as building blocks. More often than not, these mappings assume their runtimes are the only running element in the system, and if placed next to other runtimes they tend to compete for resources. Moreover, attempting to mix these models in the same program tend to have similar complication (e.g. MPI+X). Therefore, current parallel programming models tend to break programming generality as defined by Dennis in [7]. Coming up with a common abstraction which can be implemented in hardware is crucial to solve most of these issues that come from the excessive freedom given through current parallel systems.

Parallelism is hampered by its increased difficulty in programming. As previously mentioned, programmers are required to think of the interaction between workers through the use of shared memory or message passing. Message passing is tampered by its overhead and limitations to express complex programs that are also portable. In shared memory there is no implicit synchronization or coordination between threads, or hardware computational units. The programmer must build and use mechanisms (e.g. mutex primitives, critical regions and atomic operations) for synchronization of workers, coordination of tasks and assignment of workloads. An excellent explanation of this issue is presented by Edward Lee's paper "The problem with threads" [19]. These issues become more complex and prominent as the number of cores and nodes increases.

In hardware, scalability is hurt by the need to maintain the von-Neumann representation and the underlying sequential memory model needed to ease programmability. Aiming to relax the memory model becomes prohibitively expensive for the programmer as it would increase side effects during execution of programs. This could overwhelm the most avid developer, which would have to account for it on top of the requiring thread creation, synchronization and workload assignment. Multi-core systems with relaxed memory models and with non-coherent memory hierarchies have failed to succeed so far.