## PERFORMANCE, POWER, AND ENERGY TUNING USING HARDWARE AND SOFTWARE TECHNIQUES FOR MODERN PARALLEL ARCHITECTURES

by

Wei Wang

A dissertation submitted to the Faculty of the University of Delaware in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science

Summer 2016

© 2016 Wei Wang All Rights Reserved ProQuest Number: 10191145

All rights reserved

INFORMATION TO ALL USERS The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

ProQuest 10191145

Published by ProQuest LLC (2016). Copyright of the Dissertation is held by the Author.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

> ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 - 1346

# PERFORMANCE, POWER, AND ENERGY TUNING USING HARDWARE AND SOFTWARE TECHNIQUES FOR MODERN PARALLEL ARCHITECTURES

by

Wei Wang

Approved: \_

Kathleen F. McCoy, Ph.D. Chair of the Department of Computer and Information Sciences

Approved: \_

Babatunde A. Ogunnaike, Ph.D. Dean of the College of Engineering

Approved: \_\_\_\_\_

Ann L. Ardis, Ph.D. Senior Vice Provost for Graduate & Professional Education I certify that I have read this dissertation and that in my opinion it meets the academic and professional standard required by the University as a dissertation for the degree of Doctor of Philosophy.

Signed: \_\_\_\_\_

John Cavazos, Ph.D. Professor in charge of dissertation

I certify that I have read this dissertation and that in my opinion it meets the academic and professional standard required by the University as a dissertation for the degree of Doctor of Philosophy.

Signed: \_

Guang R. Gao, Ph.D. Member of dissertation committee

I certify that I have read this dissertation and that in my opinion it meets the academic and professional standard required by the University as a dissertation for the degree of Doctor of Philosophy.

Signed: \_\_\_\_\_

James Clause, Ph.D. Member of dissertation committee

I certify that I have read this dissertation and that in my opinion it meets the academic and professional standard required by the University as a dissertation for the degree of Doctor of Philosophy.

Signed: \_

Allan Porterfield, Ph.D. Member of dissertation committee

#### ACKNOWLEDGEMENTS

There are so many people that I am feeling thankful for. It would not have been possible for me to finish my graduate program without their help.

First and foremost, I would like to thank my advisor, Professor John Cavazos, for his guidance, encouragement, and support throughout my years pursuing the PhD degree. I am truly grateful to have such a considerate and caring advisor.

In the meanwhile, I would like to thank Professor Guang R. Gao, Professor James Clause, and Dr. Allan Porterfield for being on my committee and for their guidance and feedbacks on my research. I also want to specially thank Allan for being my mentor during three internships at RENCI. At RENCI, I learned a lot from Allan and built foundation for my dissertation.

Additionally, I would like to express my gratitude to Dr. Edgar Leon, who was my mentor while I was doing internship at LLNL, Professors Howie Huang and Matthew Kay for their guidance and collaboration on the first part of the dissertation, and Dr. Alexandra Jimborean for her help on understanding Decoupled Access-Execution model.

My graduate life would not be as enjoyable without my friends in and out of the lab. I would like to thank Eunjung Park, Lifan Xu, William Killian, Tristan Vanderbruggen, Robert Searles, Sameer Kulkarni, Scott Grauer-Gray, Sridutt Bhalachandra, Yuanfang Chen, Fan Yang, Yifan Peng, Xiaoran Wang, Xi Chen and Xin Cheng for their help in many aspects, from setting up experiments to substituting for lecturing, from baby sitting to job referral, etc.

I would like to thank my parents, my mother-in-law and father-in-law, and my two elder sisters for their constant love and support for me. Last but not the least, I would like to thank my wife, Fan Zhang, for always standing by me, encouraging me, supporting me, and loving me, and my daughter, Evelyn Wang, for bringing me the joy of being a father. This dissertation is dedicated to them.

## TABLE OF CONTENTS

| LIST OF FIGURES |                                        |                                      | vii<br>viii<br>ix                               |                                          |

|-----------------|----------------------------------------|--------------------------------------|-------------------------------------------------|------------------------------------------|

| C               | hapte                                  | er                                   |                                                 |                                          |

| 1               | INT                                    | RODU                                 | JCTION                                          | 1                                        |

| <b>2</b>        | BAG                                    | CKGR                                 | OUND AND RELATED WORK                           | 9                                        |

|                 | 2.1                                    | Source                               | e to Source Compilers for Loop Transformations  | 9                                        |

|                 |                                        | 2.1.1<br>2.1.2                       | PoCC and PolyOpt                                | 9<br>10                                  |

|                 | 2.2                                    | Energy                               | V Measurement Tools                             | 11                                       |

|                 |                                        | 2.2.1<br>2.2.2<br>2.2.3              | RCRdaemon       LIKWID       Intel Power Gadget | 12<br>12<br>12                           |

|                 | 2.3                                    | Power                                | Control Methods                                 | 13                                       |

|                 |                                        | $2.3.1 \\ 2.3.2 \\ 2.3.3$            | DVFSDuty Cycle ModulationPower Capping          | $\begin{array}{c} 13\\14\\16\end{array}$ |

|                 | 2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9 | Clock-<br>Concu<br>Existin<br>Autotu | Based Energy Saving Techniques                  | 16<br>17<br>17<br>18<br>19<br>20         |

| 3 |              | OPTIMIZING 2D WAVE PROPAGATION SIMULATION ON<br>MODERN COMPUTATIONAL ACCELERATORS |                                                                     |                            |  |

|---|--------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------|--|

|   | $3.1 \\ 3.2$ |                                                                                   | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$               | 22<br>24                   |  |

|   |              | $3.2.1 \\ 3.2.2 \\ 3.2.3 \\ 3.2.4 \\ 3.2.5$                                       | High Performance Computing on GPUs                                  | 24<br>25<br>26<br>29<br>32 |  |

|   | 3.3          | Result                                                                            | js                                                                  | 32                         |  |

|   |              | 3.3.1<br>3.3.2<br>3.3.3<br>3.3.4                                                  | CUDA and OpenCL Implementations                                     | 33<br>36<br>37<br>38       |  |

|   | 3.4          | Discus                                                                            | ssion                                                               | 40                         |  |

|   |              | 3.4.1<br>3.4.2                                                                    | Summary of Effective Optimizations for Different<br>Implementations | 40                         |  |

|   |              | 3.4.3                                                                             | OpenMP   OpenMP     Related Work   OpenMP                           | 42<br>43                   |  |

|   | 3.5          | Summ                                                                              | ary                                                                 | 45                         |  |

| 4 | EN           | ERGY                                                                              | TUNING USING THE POLYHEDRAL APPROACH                                | 46                         |  |

|   | 4.1<br>4.2   | Metho<br>Bench                                                                    | ods                                                                 | $\frac{46}{47}$            |  |

|   |              | $\begin{array}{c} 4.2.1 \\ 4.2.2 \\ 4.2.3 \end{array}$                            | PolybenchLULESHCardiac Wave Propagation                             | $47 \\ 48 \\ 50$           |  |

|   |              | 4.2.4                     | Experimental Setup                                                              | 51             |

|---|--------------|---------------------------|---------------------------------------------------------------------------------|----------------|

|   | 4.3          | Execu                     | tion Time and Energy Consumption Correlation                                    | 52             |

|   |              | $4.3.1 \\ 4.3.2 \\ 4.3.3$ | PolybenchModified LULESHModified LULESHThe Cardiac Wave Propagation Application | 52<br>55<br>55 |

|   |              | 4.0.0                     | The Cardiac wave Propagation Application                                        | 00             |

|   | 4.4          | -                         | edral Optimization Results on a Cardiac Wave Propagation<br>cation              | 56             |

|   |              | $4.4.1 \\ 4.4.2$          | Results on Sandy Bridge Processor                                               | 56<br>58       |

|   | 4.5          | Predic                    | ting the Optimization for Lowest Energy                                         | 58             |

|   |              | $4.5.1 \\ 4.5.2$          | Energy Prediction Model Construction                                            | 59<br>62       |

|   | $4.6 \\ 4.7$ |                           | ssion                                                                           | 64<br>69       |

| 5 |              |                           | ING OPENMP APPLICATIONS FOR ENERGY<br>NCY USING CPU CLOCK MODULATION            | 71             |

|   | $5.1 \\ 5.2$ |                           | ation                                                                           | 71<br>73       |

|   |              | $5.2.1 \\ 5.2.2$          | Loop Characterization                                                           | 74<br>75       |

|   | $5.3 \\ 5.4$ |                           | marks and Experimental Setup                                                    | 77<br>79       |

|   |              | $5.4.1 \\ 5.4.2$          | Application Power Characterization Results                                      | 79<br>86       |

|   |              | 5.4.3                     | Memory Access Density Based Runtime Energy Control                              | 90             |

|   | 5.5          | Discus                    | ssion                                                                           | 92             |

|   |              | 5.5.1                     | Frequency Transition Latency Comparison                                         | 92             |

|   |                                           | 5.5.2            | The Need for Unprivileged Energy Control                                                                           | 94         |

|---|-------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------|------------|

|   | 5.6                                       | Summ             | ary                                                                                                                | 97         |

| 6 |                                           |                  | ING SOFTWARE AND HARDWARE TECHNIQUES<br>ERGY OPTIMIZATION                                                          | 99         |

|   | $\begin{array}{c} 6.1 \\ 6.2 \end{array}$ |                  | luction                                                                                                            | 99<br>100  |

|   |                                           | $6.2.1 \\ 6.2.2$ | Combining Clock Modulation with Concurrency Throttling<br>Combining DVFS with Concurrency Throttling on IBM Power8 | 100        |

|   |                                           | 6.0.0            | Architecture                                                                                                       | 101        |

|   |                                           | $6.2.3 \\ 6.2.4$ | Polyhedral Transformation and Clock Modulation                                                                     | 101<br>102 |

|   |                                           | 0.2.4            | Cr U clock modulation under power capping constraints                                                              | 102        |

|   | 6.3                                       | Result           | S                                                                                                                  | 102        |

|   |                                           | 6.3.1            | Clock Modulation with Concurrency Throttling                                                                       | 102        |

|   |                                           | 6.3.2            | Combining software and hardware techniques on IBM Power8                                                           |            |

|   |                                           |                  | system                                                                                                             | 108        |

|   |                                           | 6.3.3            | Polyhedral Transformation with CPU clock modulation                                                                | 110        |

|   |                                           | 6.3.4            | CPU clock modulation under power capping constraints                                                               | 115        |

|   | 6.4                                       | Summ             | nary                                                                                                               | 117        |

| 7 | CO                                        | NCLU             | SION                                                                                                               | 119        |

| B | IBLI                                      | OGRA             | PHY                                                                                                                | 123        |

### LIST OF TABLES

| 1.1 | Performance, power, and energy efficiency of 6 top systems (as of June 2016) from the Top500 list and the Green500 list as well as a goal system that achieves exascale performance with 20MW of power.                                                                                                | 2  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Values to Write into IA32_CLOCK_MODULATION MSR to Achieve Duty Cycle Modulation.                                                                                                                                                                                                                       | 15 |

| 3.1 | Comparison of multiple metrics between different parallel programming implementations for the cardiac wave propagation model.                                                                                                                                                                          | 42 |

| 4.1 | This table shows the best program optimization for different input size.                                                                                                                                                                                                                               | 57 |

| 4.2 | This table shows the number of loop nests, the number of polyhedral combinations applied, and the unique number of variants for different benchmarks.                                                                                                                                                  | 60 |

| 4.3 | This table shows the results of the model when predicting the energy<br>savings of compiler transformations. The "percentage" corresponds to<br>the achievable energy savings given by the model compared to the<br>best energy savings.                                                               | 63 |

| 4.4 | This table shows the results of the model when predicting the power consumption <i>increase</i> (compared to the sequential version's power) of polyhedral transformed code. The closer the predicted power increase is to the minimal/optimal power increase, the better the transformed variant was. | 65 |

| 4.5 | Jacobi-2D Autotuning execution times                                                                                                                                                                                                                                                                   | 66 |

| 4.6 | Power for selected regions of LULESH                                                                                                                                                                                                                                                                   | 68 |

| 5.1 | This table describes the characteristics of three types of loops when varying the frequencies.                                                                                                                                                                                                         | 80 |

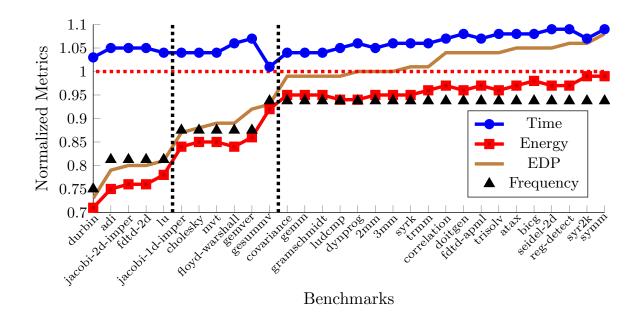

| 5.2  | This table shows the normalized time, energy, and EDP of polybench<br>pro- grams running at the best non-full speed setting. The<br>Mem-Value column shows each benchmark's memory access density.<br>Mean-High, Mean-Balanced, and Mean-Low give the average for three<br>sets of kernels divided by the vertical lines in Figure 5.7. | 87  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.3  | This table compares the execution time, energy consumption, and EDP for LULESH                                                                                                                                                                                                                                                          | 89  |

| 5.4  | This table compares the execution time, energy consumption, and EDP for miniFE                                                                                                                                                                                                                                                          | 89  |

| 5.5  | This table shows the potential benefits of multi-frequency for NPB benchmarks                                                                                                                                                                                                                                                           | 90  |

| 5.6  | Comparison of dynamic energy control with static energy control of MG and SP NPB benchmark is shown. All metrics are relative to those of static-single.                                                                                                                                                                                | 91  |

| 5.7  | This table shows DVFS frequency change latency in microseconds                                                                                                                                                                                                                                                                          | 93  |

| 5.8  | This figure shows the latency of changing clock modulation frequency in microseconds.                                                                                                                                                                                                                                                   | 94  |

| 5.9  | This table shows the overhead of executing 1 million pairs of energy changes via system call. The overhead is in seconds per million pairs.                                                                                                                                                                                             | 95  |

| 5.10 | This figure shows the execution time, energy, and power of coupled access-execution (CAE) model and decoupled access-execution (DAE) model for libQ benchmark. In DAE model, energy control APIs are called before and after the access phase.                                                                                          | 97  |

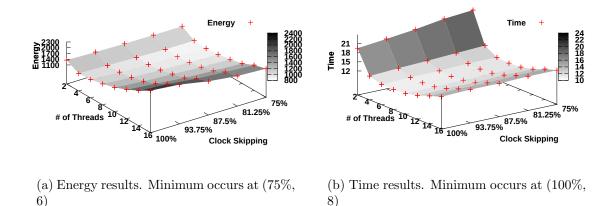

| 6.1  | LULESH with Concurrency Throttling (CT) and/or Clock Modulation (CM).                                                                                                                                                                                                                                                                   | 104 |

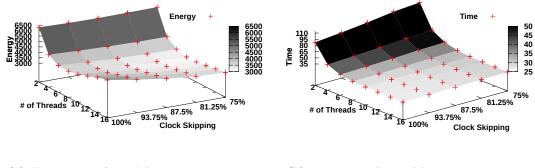

| 6.2  | miniFE with Concurrency Throttling (CT) and Clock Modulation (CM).                                                                                                                                                                                                                                                                      | 105 |

| 6.3  | Applying DVFS and Concurrency Throttling improves performance<br>and energy                                                                                                                                                                                                                                                             | 110 |

| 6.4  | The execution time, energy and power consumption of jacobi-2D benchmark with 60 Watts power cap and different DC setting                                                                                                                                                                                                                | 116 |

| 6.5 | The execution time, energy and power consumption of jacobi-2D benchmark with different DC setting but no power cap                          | 116 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.6 | The execution time, energy and power consumption of the fastest jacobi-2D program variants with different DC setting and 60 Watts power cap | 117 |

| 6.7 | The execution time, energy and power consumption of the fastest jacobi-2D program variants with different DC setting but no power cap.      | 117 |

### LIST OF FIGURES

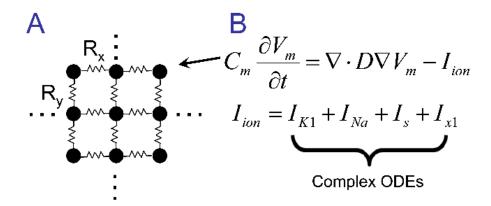

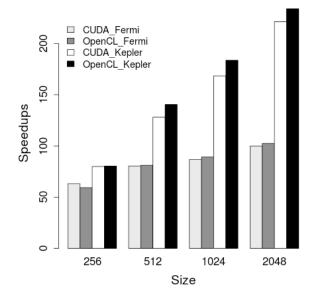

| 3.1 | (A): Cardiac tissue is modeled as a large geometrical network of nodes that are electronically coupled (B): The electrical potential of the cardiac cell membrane at each node is represented as a large set of partial differential equations                                                           | 23 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

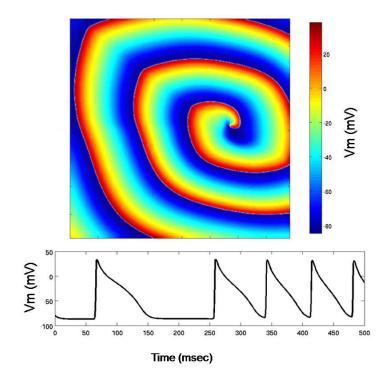

| 3.2 | Simulation of a single rotor. Top: An image showing cardiac electrical wave propagation as spatial fluctuations of transmembrane potential. A single rotating wave (rotor) is shown. Bottom: Action potentials at one node are shown as the temporal variation of the transmembrane potential at a node. | 27 |

| 3.3 | Simulation of rotor breakup and fibrillatory activity. Top: An image<br>of transmembrane potential showing complex wave activity. Bottom:<br>Action potentials at one node are shown as the temporal variation of<br>the transmembrane potential at a node                                               | 28 |

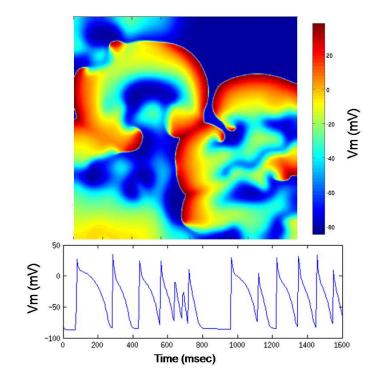

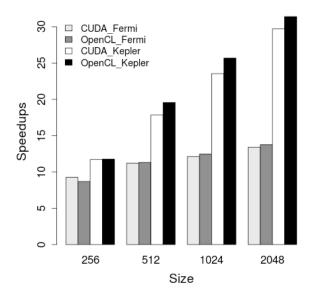

| 3.4 | Speedups from running on the Fermi-architecture Tesla C2050 GPU<br>and the Kepler architecture Tesla K20 GPU using OpenCL and<br>CUDA for reentrant activity (one rotor) simulation                                                                                                                      | 34 |

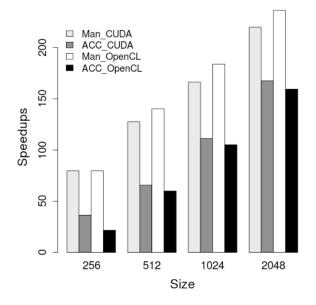

| 3.5 | Speedups of hand-written GPU code (Man_CUDA, Man_OpenCL) over the sequential baseline vs. speedups of OpenACC targeting CUDA and OpenCL (ACC_CUDA, ACC_OpenCL) over the same baseline. All GPU codes were run on the Kepler GPU                                                                          | 36 |

| 3.6 | Speedups on Fermi GPU (NVIDIA C2050) and Kepler GPU (NVIDIA K20) over the 8 core OpenMP implementation. Reentrant activity (one rotor) was simulated.                                                                                                                                                    | 38 |

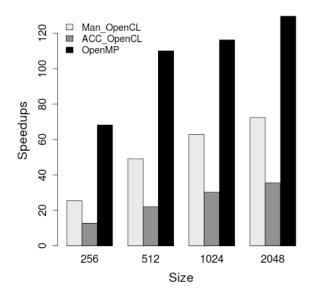

| 3.7 | Speedups on MIC-architecture Xeon Phi coprocessor using<br>hand-written OpenCL, OpenACC-generated OpenCL, and OpenMP<br>implementation over the sequential implementation. Reentrant<br>activity (one rotor) was simulated.                                                                              | 39 |

|     | activity (one rotor) was simulated                                                                                                                                                                                                                                                                       |    |

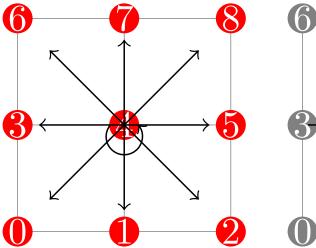

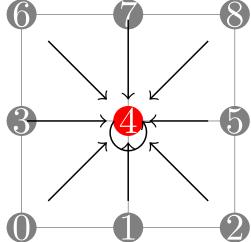

| 3.8 | This figure shows two ways of executing a critical piece of code of the model on GPUs. Suppose a GPU thread is mapped to the center node. This code involves updating each model node's potential with its neighboring nodes' potentials from a previous iteration | 41 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

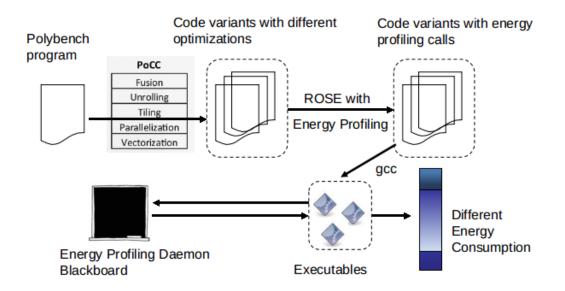

| 4.1 | The workflow of obtaining energy consumption of polyhedral optimized Polybench programs.                                                                                                                                                                           | 49 |

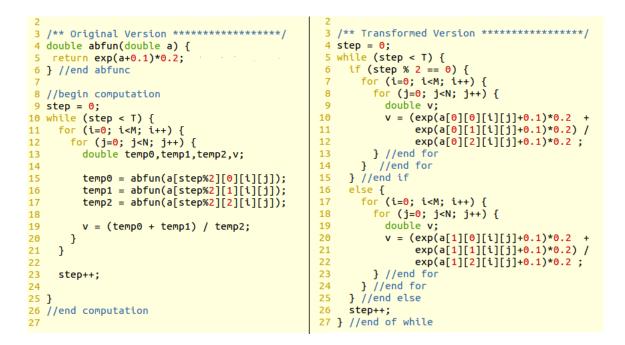

| 4.2 | A simplified version of the original LULESH loop nest and the same<br>loop nest transformed using loop unswitching                                                                                                                                                 | 51 |

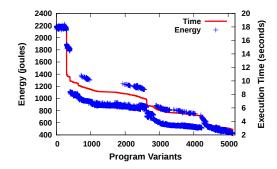

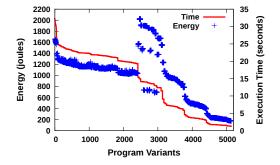

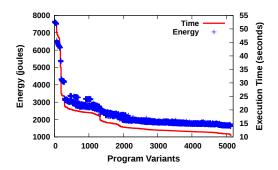

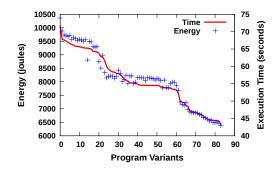

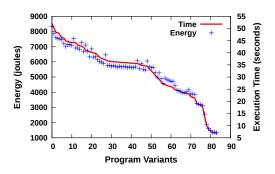

| 4.3 | Execution time and energy consumption correlation of Polybench programs (covariance, 2mm, and seidel-2d) and LULESH                                                                                                                                                | 54 |

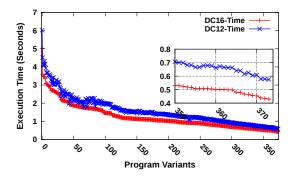

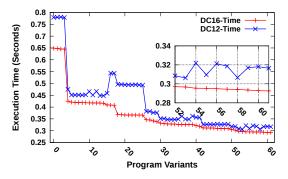

| 4.4 | Graphs showing the correlation between the execution time and the energy consumption of $brdr2d$ on a Sandy Bridge processor and on a Xeon Phi architecture (both sorted by execution time)                                                                        | 55 |

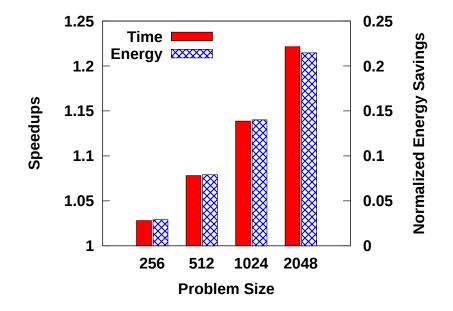

| 4.5 | Graph showing the performance improvement and energy savings of<br>the optimal program variant over the baseline OpenMP<br>implementation for different problem size on Sandy Bridge Processor.                                                                    | 57 |

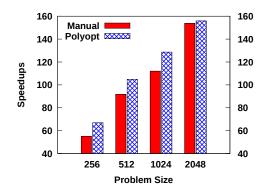

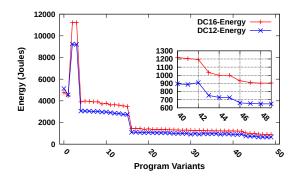

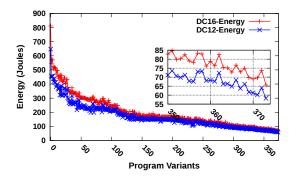

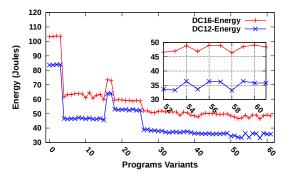

| 4.6 | Polyhedral Optimization Results on MIC architecture                                                                                                                                                                                                                | 59 |

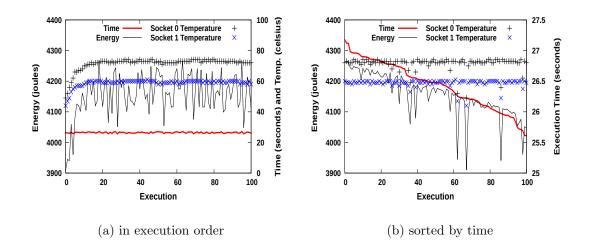

| 4.7 | Time/Energy/Temperature for 100 runs of LULESH                                                                                                                                                                                                                     | 68 |

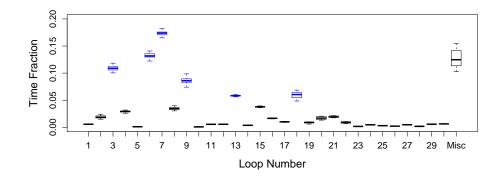

| 4.8 | Execution time and power consumption of LULESH parallel regions                                                                                                                                                                                                    | 70 |

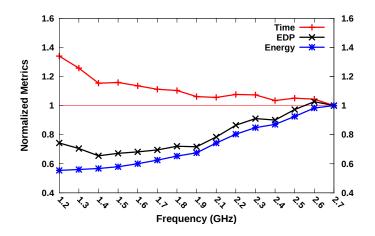

| 5.1 | This figure shows the energy, Time, and EDP of a memory-intensive LULESH loop when varying frequency using DVFS. Values normalized to 2.7GHz                                                                                                                       | 72 |

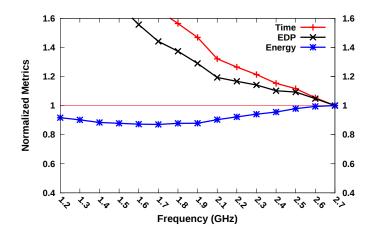

| 5.2 | This figure shows the energy, Time, and EDP of a compute-intensive LULESH loop when varying frequency using DVFS. Values normalized to 2.7GHz.                                                                                                                     | 73 |

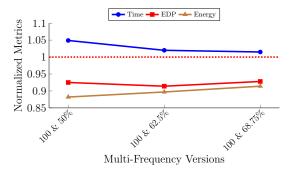

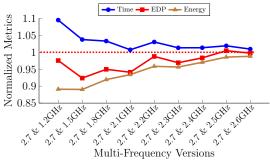

| 5.3 | This figure shows normalized metrics of multi-frequency execution of LULESH application over the default single frequency execution. 100% and 2.7GHz are the default single-frequency execution for clock modulation and DVFS, respectively.                       | 76 |

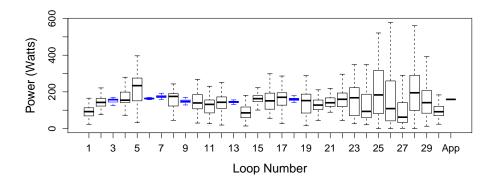

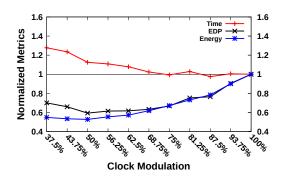

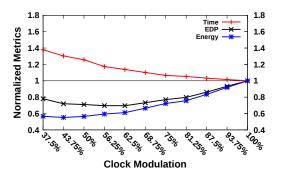

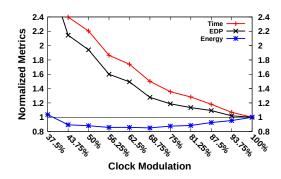

| 5.4 | Characteristics of high memory access density loops in LULESH, MG benchmark, fdtd-2d Polybench, and jacobi-2d Polybench are shown. The normalized metrics are energy, time, and energy-delay product (EDP). Lower is better. The baseline is 100% clock modulation setting. | 81  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

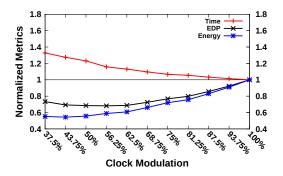

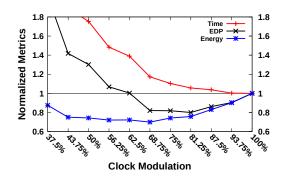

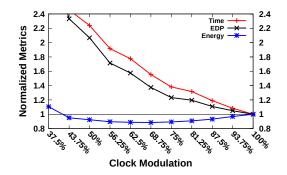

| 5.5 | Loops with balanced memory access and computation in LULESH,<br>miniFE, cholesky Polybench, and brdr2d realistic application are<br>shown. The normalized metrics are energy, time, and EDP (lower is<br>better). The baseline is 100% clock modulation setting             | 83  |

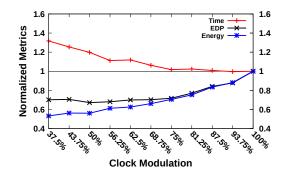

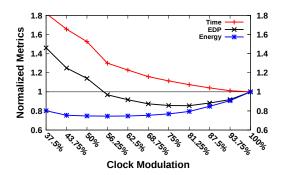

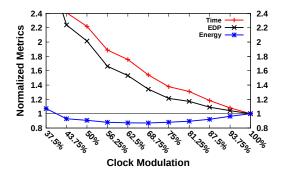

| 5.6 | This figure shows low memory access loops in four benchmarks:<br>LULESH, miniFE, doitgen Polybench, and covariance Polybench.<br>The normalized metrics are energy, time, and EDP (lower is better).<br>The baseline is 100% clock modulation setting.                      | 85  |

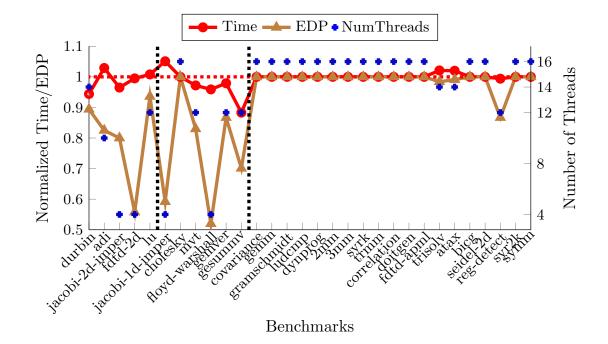

| 5.7 | Graph showing the normalized time, energy, and EDP of polybench programs running at the best non-full speed setting                                                                                                                                                         | 86  |

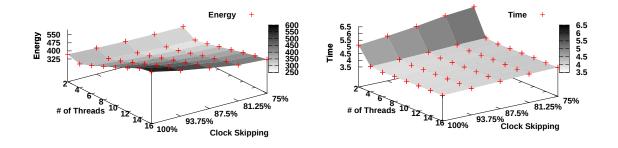

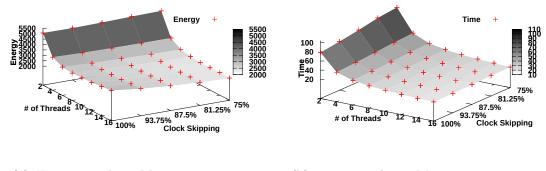

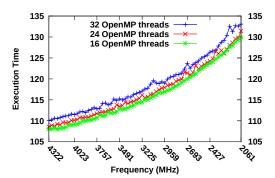

| 6.1 | fdtd-2d Polybench results when applying both concurrency throttling and clock modulation.                                                                                                                                                                                   | 102 |

| 6.2 | LULESH results when applying both concurrency throttling and clock modulation.                                                                                                                                                                                              | 103 |

| 6.3 | miniFE results when applying both concurrency throttling and clock modulation.                                                                                                                                                                                              | 105 |

| 6.4 | brdr2d results when applying both concurrency throttling and clock modulation.                                                                                                                                                                                              | 106 |

| 6.5 | Graph showing the time and EDP of Polybench running with a thread configuration that achieves the best energy efficiency                                                                                                                                                    | 107 |

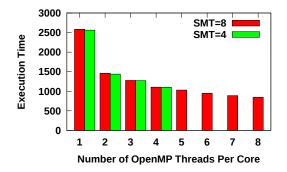

| 6.6 | Comparing the application performance with varying number of threads per core and SMT settings                                                                                                                                                                              | 108 |

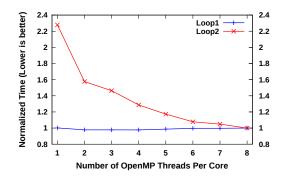

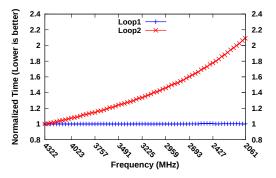

| 6.7 | miniFE contains loops that respond differently when applying concurrency throttling and DVFS                                                                                                                                                                                | 109 |

| 6.8 | miniFE contains loops that respond differently when applying concurrency throttling and DVFS                                                                                                                                                                                | 110 |

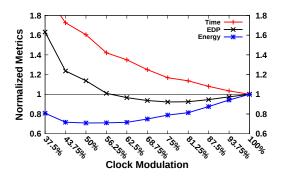

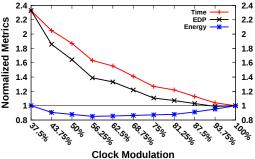

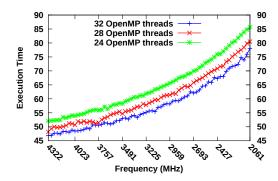

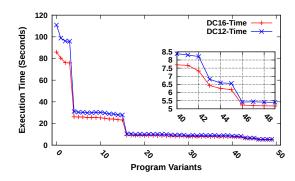

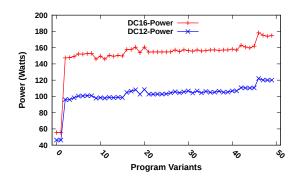

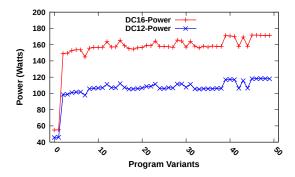

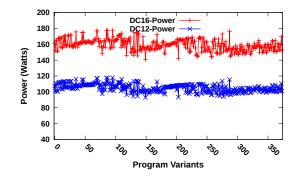

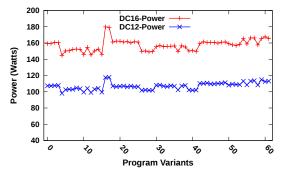

| 6.9  | This figure shows the impact of changing Duty Cycle Modulation on<br>the execution time of compiler transformed versions of the jacobi-2D,<br>fdtd-2D, 2mm and gesummv polybench kernels     | 111 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

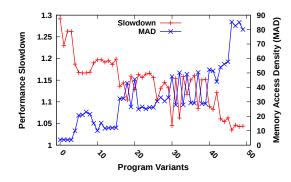

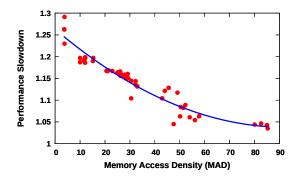

| 6.10 | This figure shows the correlation between the Memory Access Density metric and the performance slowdown of jacobi-2D benchmark.                                                              | 113 |

| 6.11 | This figure shows the impact of changing Duty Cycle Modulation on<br>the power consumption of compiler transformed versions of the<br>jacobi-2D, fdtd-2D, 2mm and gesummv polybench kernels  | 114 |

| 6.12 | This figure shows the impact of changing Duty Cycle Modulation on<br>the energy consumption of compiler transformed versions of the<br>jacobi-2D, fdtd-2D, 2mm and gesummv polybench kernels | 115 |

#### ABSTRACT

As the high-performance computing (HPC) community continues the push towards exascale computing, power consumption is becoming a major concern for designing, building, maintaining, and getting the most out of supercomputers. Energy efficiency has become one of the top ten exascale system research challenges. Meeting the goal of exascale performance with 20 Megawatts of power limit requires performance, power, and energy optimization techniques at all levels, from the hardware to the application. In the meanwhile, although advances in parallel architectures promise improved peak computational performance, the use of software tools to drive parallelism of the hardware still requires expertise that is not widely available. Domain scientists are faced with a challenge to efficiently port applications to new parallel architectures like Nvidia GPUs and Intel Many-Integrated Core (MIC) accelerators. The fact that an increasing number of supercomputers are going to contain accelerators poses more challenge to application developers, who will need to get their applications ready for the supercomputers.

In this dissertation, we began with the study on how to achieve both automatic parallelization using OpenACC and enhanced portability using OpenCL. We applied our parallelization techniques on GPUs as well as an Intel MIC-architecture accelerator to reduce the running time of 2D wave propagation simulations. The performance and programmability of CUDA, OpenCL, OpenACC, and OpenMP implementations of the wave propagation simulation are compared. Compared to CUDA and OpenCL, we believe that OpenACC is preferable for domain scientists because programmers can parallelize their code using simple directives, and therefore it speeds up the process of parallelizing applications. OpenACC is shown to be able to achieve comparable performance as CUDA and OpenCL on GPUs with much reduced coding effort. Our OpenMP implementation outperforms OpenCL and OpenACC on the Intel MIC accelerator. Emerging software developments like the OpenACC facilitate exploiting application parallelism offered by evolving hardware architecture. Our method of using OpenACC, OpenCL, and OpenMP to achieve efficient and effective parallelization on different accelerators can be generally applied to benefit other domains.

For the energy tuning problem, we tackle the problem from using software techniques first. We integrated an energy measurement framework to an existing polyhedral transformation framework called PoCC. Loop transformations supported by PoCC have been shown to be effective in optimizing the performance of small kernels. However, there have been few studies on how these transformations affect the power and the energy. The energy measurement framework allows exploring the relationship between tuning for power/energy and tuning for performance. A high correlation of energy/performance in PoCC is observed but tuning for power is different from tuning for execution time. We constructed predictive models that achieved high prediction accuracy. In addition, we also demonstrate the potential of polyhedral transformations in optimizing the 2D cardiac wave propagation application for both performance and energy.

Then, we propose to minimize energy usage without impacting the performance of HPC applications from using hardware techniques. We developed energy optimization techniques that did not only reduce power, but also Energy-Delay Product (EDP) and in some cases even Energy-Delay-Squared Product (ED<sup>2</sup>P). We took advantage of the low transition overhead of CPU clock modulation and applied it to fine-grained OpenMP parallel loops. The energy behaviour of OpenMP parallel regions is first characterized by the memory access density. By characterizing memory access density, the best clock modulation setting is determined for each region. Finally, different CPU clock settings are applied to the different loops within the same application. The resulting multi-frequency execution of OpenMP applications achieved better energy efficiency than any single frequency setting.

In the last chapter of this dissertation, we combined software and hardware

techniques to obtain better energy efficiency for HPC applications. In particular, on Intel Sandy Bridge architecture we applied concurrency throttling, i.e., reducing the number of threads needed by an OpenMP application, with CPU clock modulation and on IBM Power8 architecture we applied concurrency throttling with DVFS. In both cases we observed improved energy efficiency. Lastly, we combined polyhedral compilation techniques with CPU clock modulation and evaluated their interactions under a power-capped environment.

## Chapter 1 INTRODUCTION

As the high-performance computing (HPC) community continues the push towards exascale computing, power consumption has become a major concern for designing, building, maintaining, and getting the most out of supercomputers and energy efficiency has become one of the top ten exascale system research challenges [93]. State-of-the-art technologies still have a big gap in achieving desired energy efficiency in terms of performance per Watt. Table 1.1 lists the performance (in TFLOPS), power (in KiloWatts), and energy-efficiency (in GFLOPS per Watt) of the three fastest supercomputers from the Top500 list [2] and the three most energy-efficient supercomputers from the Green 500 list [1]. Also shown in the table is a goal system that attains exascale performance with the 20MW power limit set by the HPC community [9]. Meeting the goal of exascale performance and the goal of 20 Megawatts of power requires an energy efficiency of fifty GFLOPS/watt (billions of operations per second per watt). However the world's "greenest" Shoubu supercomputer from RIKEN has not yet surpassed seven GFLOPS/Watt. The immediate two runner-ups achieved just a little over six GFLOPS/Watt. The world's fastest supercomputer Sunway TailhuLight has reached 93 Petaflops but its energy efficiency is about six GFLOPS/Watt. The second fastest supercomputer Milkyway-2 has reached 33 Petaflops of sustained performance but is drawing the power at the rate of almost 20 Megawatts, resulting in an energy efficiency of only 1.901. Titan, the third fastest supercomputer is only about 10% more energyefficient than Milkyway-2. Next-generation supercomputers step closer to the goal but continuous efforts are needed to further optimize the performance and power. Summit and Sierra, two supercomputers that are staged to replace Titan and Sequoia respectively, will reach more than 100 Petaflops (one tenth of 1 Exaflops) peak computation

| System                          | Performance (TFLOP/s) | Power (KW) | GFLOPS/W |

|---------------------------------|-----------------------|------------|----------|

| Exascale Goal System            | 1,000,000             | 20,000     | 50       |

| Top500 NO.1 (Sunway-TaihuLight) | 93,014.6              | 15,371     | 6.051    |

| Top500 NO.2 (Milkyway-2)        | 33,862.7              | 17,808     | 1.901    |

| Top500 NO.3 (Titan)             | 17,590.0              | 8,209      | 2.143    |

| Green500 NO.1                   | 1001.0                | 149.99     | 6.674    |

| Green500 NO.2                   | 290.5                 | 46.89      | 6.195    |

| Green500 NO.3                   | 93,014.6              | 15,371     | 6.051    |

**Table 1.1:** Performance, power, and energy efficiency of 6 top systems (as of June 2016) from the Top500 list and the Green500 list as well as a goal system that achieves exascale performance with 20MW of power.

rate [36]. Summit will draw 10 MW of power, i.e. 10% more than Titan [67]. Addressing the power consumption issue requires developing energy efficiency techniques at all levels, from the hardware to the application. Optimizing HPC applications for energy has become as important as optimizing for performance. Controlling an application's energy use running on increasingly powerful compute nodes will continue to be an important concern.

Before tuning an application for energy efficiency, it is necessary to understand how energy consumption optimization is related to traditional performance (i.e., execution time) optimization. Knowledge of the relationship between performance and energy can guide the tuning effort on pre-exascale and exascale systems. For most scientific applications, nested loops consume a significant portion of the total running time. When tuning an application for better performance and energy usage, some combination of loop optimizations, including loop tiling, loop unrolling, and loop fusion, are usually performed on the program along with auto-parallelization. Determining which set of optimizations produces the best results is challenging. Polyhedral auto-tuning frameworks have shown promising results at simplifying that effort [70, 68, 69] for small computation kernels, such as the Polybench programs [77]. The foundation of our autotuning framework is a polyhedral compiler, capable of generating thousands of program variants with the same semantics as the original program. In order for programs to be auto-tuned using a polyhedral framework, the original program should contain Static Control Parts (SCoPs). Polybench is a suite of programs containing SCoPs. We added energy measurement capability on top of an existing performance auto-tuning framework to study the relationship between optimization for performance and for energy. In this dissertation work, we use the Resource Centric Reflection daemon tool (RCRtool/RCRdaemon) developed at RENCI [74], to measure energy consumption at a fine granularity for any OpenMP program. Fine-grain measurements enable attribution of energy consumption to particular application regions and even to individual lines of codes. This allows an accurate study of the correlation between execution time and energy consumption of an application. If the correlation study reveals that there is no or little correlation between execution time and energy consumption of program variants, then the machine learning model for predicting the best performing variant will not be suitable for predicting the version that consumes the minimum amount of energy. On the other hand, if a strong correlation between execution time and energy consumption exists, then the auto-tuning framework for sifting out the best optimizations can be extended to select the program version that consumes the least amount of energy.

Although polyhedral compilers are powerful in generating various code versions for specially written small kernels like those found in the Polybench, their restrictive requirements (SCoPs only) usually limit their application in optimizing larger and realistic applications. One reason is that many applications do not contain SCoPs by default. It is not uncommon for scientific codes to include indirect memory accesses. However no indirect memory access is allowed in a SCoP therefore polyhedral compilers would not be capable of dealing with applications with such code characteristics. Fortunately there are realistic applications that are amenable to polyhedral compilers. Such applications perform complex simulations without using a lot of branching and indirect memory access. This dissertation will show the effectiveness of using polyhedral compilers to optimize a wave propagation in simulation application for performance. This realistic application simulates the cardiac wave propagation in a 2D grid and is used for cardiac arrhythmia research. From our experience of polyhedrally optimizing a realistic application, we hypothesize that a large number of kernels from realistic scientific applications can benefit from applying source-to-source transformations using polyhedral compilers.

Several current and future top supercomputers feature accelerators that represent the state-of-the-art parallel architecutre innovations. For example, the Titan supercomputer features hybrid parallel architecture consisting of multi-core AMD Opteron CPU and Nvidia Kepler K20x GPU. Two future supercomputers (Summit and Sierra) will both include IBM Power9 multi-core CPUs and Nvidia Volta GPUs. On Summit, more than 90% of floating point calculation power is expected to come from Volta GPUs. The Milkyway-2 supercomputer contains Intel Xeon Phi coprocessors, which are Many-Integrated-Core (MIC) architecture accelerators. Several future supercomputers like Aurora and Theta will include next-generation Xeon Phi processors [5]. It is worthwhile to prepare applications for getting good performance out of the GPUs or Xeon Phi accelerators found on supercomputers, using various appropriate tools. CUDA, OpenCL, and OpenACC are three major programming languages that target GPUs. New developments on the OpenMP standard include the "target" construct to support execution on GPUs. However, these new developments are still evolving, and they are not as mature as OpenACC. OpenMP code traditionally runs only on multi-core CPU architectures but the MIC architecture additionally supports OpenMP. CUDA and OpenCL are low-level GPU programming languages while OpenACC and OpenMP are high-level, directive-based language and language extension. Compared to CUDA and OpenCL, OpenACC and OpenMP are better for domain scientists because programmers can parallelize their code using simple directives, and therefore it speeds up the process of preparing applications for supercomputers. OpenCL and OpenACC are portable languages and extensions in that the code generated by these languages can run on both Nvidia GPUs and the Intel MIC architecure. OpenCL is known for its portability and an OpenACC compiler can generate OpenCL code that targets different platforms, including Intel Xeon Phi nodes. In this dissertation, the aforementioned wave propagation simulation application is used to show how different programming languages and language extensions can help prepare applications for execution on modern parallel architectures, especially the newest HPC systems that contain accelerators. In addition, performance and programmability of CUDA, OpenCL, OpenACC, and OpenMP implementations of the cardiac wave propagation simulation are compared. OpenACC is shown to achieve comparable performance as CUDA and OpenCL on GPUs with much less code. Our OpenMP implementation outperforms OpenCL and OpenACC on an Intel Xeon Phi node.

In our research, we found that performance optimizations that improve execution time save energy as a by-product of the improved performance. This is referred to as a "race-to-halt" strategy. Other than this "race to halt" strategy that focuses on performance improvement, research has employed Dynamic Voltage and Frequency Scaling (DVFS) techniques to save energy. Ge et al. divided applications into fixed intervals and determined a suitable frequency for each interval by using performance counters [28]. Other work looked at applying DVFS during communication phases or non-critical execution paths of MPI applications to lower power consumption without affecting performance [96, 94, 95, 25, 99]. All of these approaches applied DVFS to the coarse-grain phases of the application. For OpenMP code, parallel regions as identified by the "parallel" construct naturally divide an application into fine-granularity phases, especially for code that involves multiple time-steps. None of the aforementioned DVFS approach applied energy control on a per-loop basis. This was likely due to the overhead of switching the frequency using DVFS prevented it from being used for small code regions.

Another method to reduce energy consumption of CPUs is CPU clock modulation, also known as Duty Cycle Modulation, CPU throttling, or CPU clock skipping, which squashes cycles in the CPU clock without changing the real frequency [96, 37, 110]. Using this technique allows individual cores to have the effective clock frequency reduced, without changing the voltage or the memory system's clock. The advantage of CPU clock modulation over DVFS is the much lower transition overhead [76], since no voltage stabilization must occur. In addition, CPU clock modulation can be applied on top of DVFS to provide more fine-grained energy control knobs that are otherwise available with DVFS. When the CPU has significant pipeline stalls or idle instructions, clock modulation reduces the energy required during the stalls.

Like DVFS, applying clock modulation to every parallel region can slow down execution and lead to increased energy consumption. By characterizing OpenMP parallel loops as compute-bound or memory-bound first, the appropriate clock modulation setting can be applied to each appropriate loop. Applications can have multiple parallel loops with different memory access densities. These types of applications have loops that prefer distinct frequency settings per loop that results in the minimum energy or energy-delay product (EDP). Applications with a variety of different classes of regions have the potential of benefitting from fine-grained per-loop clock modulation to conserve energy without performance degradation.

For loops with high/medium memory access density, reducing the frequency eliminates some of the energy during stalled pipeline cycles. For loops with low memory access density, setting the frequency to the maximum can avoid the unnecessary delay of computation. Using the best frequency for different loops can have a lower energy/EDP than any single frequency execution setting. A multi-frequency setting profits from saving energy during CPU stalls (e.g. during cache misses) and maximizing computation otherwise.

Another technique we investigated was concurrency throttling [49, 76], which reduces the number of hardware threads being used, thus saving energy when parts of the system are saturated. It can be combined with clock modulation to further reduce energy consumption for some application phases on Intel architectures. As mentioned earlier, Summit and Sierra supercomputers both feature IBM Power9 architecture and Nvidia's Volta GPU architecture. We believe it worthwhile to test the combined software techniques (concurrency throttling) and hardware techniques (energy control) on the Power architecture. At the time this dissertation research was performed, the IBM Power9 was not in production, therefore this dissertation investigated its predecessor, the Power8 architecture. Similar to the Power9, the Power8 also featured 8-way simultaneous multithreading (SMT-8). However, since the Power8 did not support the CPU clock modulation hardware feature, we combined per-core DVFS with concurrency throttling<sup>1</sup>.

Future data centers and supercomputers will have to address the challenge of running applications with limited power envelope due to budget concerns. This has prompted new power management features in new parallel architectures. As an example, power capping is a built in concept in the overall architecture design of IBM Power8 architecture [24]. Optimizing application performance on power constrained HPC systems arises as a new challenge. Power capping usually sets stage for power shifting which redistributes power resources to different components within a compute node [48]. In addition to realize intelligent balancing of critical power resource, power capping can be applied for thermal control. In this dissertation, we study how applications perform under a set power limit on Intel SandyBridge architecture. Unlike IBM Power architecture which relies an On Chip Controller (OCC) to cap the power consumption implicitly according to thermal control algorithms, power capping on Intel platforms can be done explicitly via privileged instructions. In addition, other power management techniques like DVFS and CPU clock modulation can be applied on top of power capping. Combined effects of power capping and clock modulation techniques are investigated for several benchmarks in this work. We also combined polyhedral compilation with clock modulation technique to find opportunities where polyhedral optimized code could be further optimized for energy and energy efficiency (e.g. EDP).

The main contributions of this dissertation are as follows. First, we parallelized and optimized a realistic scientific application on several parallel architectures using different programming tools. The lessons learned can benefit a broad range of developers who aim to make their applications performant and energy efficient on supercomputers involving accelerators like the Nvidia GPUs and the Intel accelerators. Second,

<sup>&</sup>lt;sup>1</sup> On Intel Sandy Bridge architecture, DVFS is not per-core but per-socket.

to tackle the energy optimization issue, we studied the energy and time correlation of programs in a polyhedral autotuning framework. Tuning for time with polyhedral transformations can be used as a proxy for tuning for energy. A predictive model for energy is also developed and verified to have good accuracy. Then, we studied the energy characteristics of application loops in the context of being able to control machine power usage. Although a whole application might prefer "racing to halt" to get the best energy efficiency, the individual loops can have different preferences based on their memory density. Several mini-applications are executed in a multi-frequency fashion (i.e. different loops are executed at different frequencies using CPU clock modulation) to achieve the best energy-delay trade-off. Third, we show that combining hardware techniques like CPU clock modulation and DVFS with software techniques like concurrency throttling and polyhedral compilation achieves better energy and EDP improvement. Our experiences using IBM Power8 architecture to evaluate its DVFS features are encouraging for the OpenPower community. In addition, our experiments with power capping, CPU clock modulation, and polyhedral compilation provide insights on how applications would perform on future power constrained systems.

The rest of the dissertation is organized as follows. Chapter 2 gives the background necessary to understand the research in this dissertation. Chapter 3 discusses the parallelization and optimization of 2D wave propagation simulation on modern computational accelerators, including GPUs and Xeon Phi. Chapter 4 uses the polyhedral framework to evaluate execution time and energy consumption correlation. A predictive model for energy that drives polyhedral optimizations applied to parallel application is also covered. Chapter 5 shows how we utilize the energy control hardware methods to optimize applications for energy. Chapter 6 combines software techniques and hardware techniques used in previous chapters to further optimize benchmarks for energy on both Intel and IBM multicore architectures. Evaluation of benchmark performance in power-capped environment is also performed in this chapter. Chapter 7 concludes the dissertation.

#### Chapter 2

#### BACKGROUND AND RELATED WORK

This chapter introduces the tools and techniques used in this dissertation such as loop transformation tools, energy measurement tools, and energy control methods. State-of-the-art studies that used these tools are discussed.

#### 2.1 Source to Source Compilers for Loop Transformations

The Polyhedral Compiler Collection (PoCC)[79], a source-to-source polyhedral compiler, was frequently used in this dissertation. This source-to-source compiler was used in Chapter 4 and Chapter 6 to generate program variants with different optimizations. It was also used in Chapter 4 to optimize application performance. Other compilers that can perform polyhedral source-to-source transformations include CHiLL and Orio.

#### 2.1.1 PoCC and PolyOpt

PoCC requires that programs contain Static Control Parts (SCoP)[8, 23, 29] so that polyhedral transformations can be applied. A SCoP consists of a set of consecutive statements, which usually form a loop nest. The loop bounds, if statement conditionals, and array accesses in the loop nest should all be affine functions of the loop iterators and global parameters. For example, a valid affine expression for a loop bound in a SCoP with two loops iterators i,j and two parameters N,P will be of the form  $a \cdot i + b \cdot$  $j + c \cdot N + d \cdot P + e$ , where a,b,c,d,e are arbitrary (possibly 0) integer numbers. The following are examples that break the SCoP property:

• Non-affine for initialization or test condition, e.g., for(j = 0; j < i \* i; + i).

- if conditionals involving loop iterators that form a non-affine expression, e.g., if (i \* j == 0).

- if conditionals involving variables that are not a loop iterator or a parameter, e.g., if (A[i][j] == 0).

- Non-affine array access, e.g., A[j % i] or A[B[i]].

In practice, code with excessive use of local variables, can make the polyhedral compiler take a very long time to transform programs.

Polybench is a collection of programs that contain SCoPs and thus can be optimized with a polyhedral compiler. Inside the compiler, each SCoP is represented by two matrices, which correspond to the loop nests' iteration domain as well as the statements' dependencies. Loop transformations on such programs are equivalent to manipulating such matrices. The transformed matrices can be converted back to semantically equivalent, but optimized code.

We used PolyOpt (a Polyhedral Optimizer for the ROSE compiler) [78] to automatically detect SCoPs in applications. PolyOpt is based on PoCC, but integrated into the ROSE compiler. Aside from its capability to extract SCoP regions in an automatic way, it fully supports polyhedral analysis and optimizations. PolyOpt supports loops fusion, loop tiling, thread-level parallelization and vectorization. PolyOpt has better support for side-effect free program features like math functions[8] and allows some function calls within a SCoP. PolyOpt, although a powerful polyhedral compiler, still may not be able to extract any SCoPs because of structural impediments of source codes. Changes to the program may be required to expose the SCoPs for PolyOpt, before loop transformations, parallelization, and vectorization can occur.

#### 2.1.2 Other source-to-source compilers

Other source-to-source polyhedral compilers include CHiLL [15], Orio [61], PPCG [101], LooPo [31], PLUTO [12] and R-stream[87] etc. CHiLL takes in the original code and a transformation script as input and outputs a set of alternative implementations. The transformation script, also called transformation recipe, describes how to optimize the code. For example, a CHiLL transformation script may include loop permutation, loop tiling, and loop unrolling etc. Orio has similar functionality in transforming programs. Instead of taking in a stand-alone transformation recipe, it takes in the original code with annotated text for loops of interest. PPCG is a polyhedral parallel code generator that translates sequential static control code for parallel execution on a modern GPU. LooPo and PLUTO both generate parallelized code for execution on modern shared-memory systems. PLUTO is included in POCC. R-stream is a commercial source-to-source compiler from Reservoir Labs. For our energy/performance correlation study, CHiLL, Orio, PPCG, and LooPo could potentially be used instead of PoCC. However, we chose PoCC with PLUTO because it has been extensively tested on our benchmarks of interest, including the Polybench.

#### 2.2 Energy Measurement Tools

Traditional energy measurement tools require hardware instrumentation and provide coarse grained energy measurement. In contrast, software energy measurement is more fine-grained. The Intel Sandy Bridge and Haswell architectures allow users to track energy usage through the Running Average Power Limit (RAPL) interface [37]. Energy consumed by the chip can be tracked by a Model Specific Register (MSR), specifically the MSR\_PKG\_ENERGY\_STATUS performance counter. This counter is frequently updated and counts the energy in 15.3 micro-Joule (i.e.  $1/2^{16}$  Joule) units on Sandy Bridge architectures and 61.2 micro-Joule (i.e.  $1/2^{14}$  Joule) units on Haswell architectures. Based on RAPL, different software tools were developed to monitor power usage of applications. In this dissertation work, we use RCRdaemon [75] to monitor application energy. Other tools that can measure application energy based on RAPL include LIKWID [100] and Intel Power Gadget[39]. The accuracy of these tools relies on the exactness of RAPL. Hähnel *et al.* reported the identical curve characteristics comparing RAPL with external measurement[32] while presenting their HAECER framework for short-term energy measurements using RAPL.

#### 2.2.1 RCRdaemon

The RCR daemon runs at supervisor level to access the hardware counters through the MSR performance counters. For each monitored counter, it writes the current value of the counter at least 1000 times a second into a shared-memory data structure. This "blackboard" structure provides a hierarchical view of the system where various current performance information is stored. The storage is only 8KB. The hardware MSR\_PKG\_ENERGY\_STATUS counter is only 32 bits and can overflow in as little as a couple of minutes. The RCR daemon detects the overflow and supplies a 64 bit value with the upper 32 bits being the number of overflows since RCR daemon instantiation. The stored information is in shared memory and is available to any OpenMP applications through a simple API that delineates a code region for measurement with a start and end call. Each region is identified by its file name and line number. If a region is executed multiple times, the energy is summed across all executions. All energy information is available during application shutdown. The execution time increase from continuous monitoring of a 400-second OpenMP application is observed to be less than 8%.

#### 2.2.2 LIKWID

LIKWID contains a set of command-line lightweight performance tools. It offers likwid-powermeter to access RAPL energy counters and query Turbo mode steps on Intel processors. It does not export an energy library for direct application invocation.

#### 2.2.3 Intel Power Gadget

Like LIKWID, the Intel Power Gadget can also output current energy information by querying RAPL energy counters. RCRdaemon differs from both the Intel Power Gadget and LIKWID in that it manages energy information in a way that provides access to all applications This is supported by the daemon querying the counters frequently and calculating the energy as well as the APIs granting all applications access to the energy information.

#### 2.3 Power Control Methods

Modern Intel CPU architectures provide three mechanisms to control power usage. They are Dynamic Voltage and Frequency Scaling (DVFS), Duty Cycle Modulation (DCM, also called Clock Modulation), and Power Capping. Similar to the APIs that get the energy consumption information, energy control API calls are developed and inserted into the source code to control the voltage and frequency for DVFS, the clock modulation for DCM, and the power cap for Power Capping.

#### 2.3.1 DVFS

DVFS refers to changing the frequency along with the paired voltage to put machines into low-power states. For a given machine, only a limited set of frequency/voltage pairs are supported. Users can invoke DVFS by writing the desired frequency value to a file on the file system. The driver, i.e., acpi-cpufreq, is responsible for detecting this change of frequency and for making the transition. Note that even though the users only specify the change of frequency, voltage values will be automatically changed. The frequency/voltage transition latency as well as the available set of frequencies can be looked up from files on the file system when the DVFS driver is enabled. As an example, to set all CPU cores to 1.2GHz, a user can invoke the following command that writes the frequency value (1200000 KHz) to the files (scaling\_setspeed) associated with each cpu core.

#### echo 1200000|tee /sys/devices/system/cpu/cpu\*/cpufreq/scaling\_setspeed

The above method of changing DVFS utilizes a shell script and is relatively coarsegrained. A faster method of enabling DVFS changes is to open the scaling\_setspeed file and overwrite its contents.

In order to achieve dynamic change of voltage and frequency scaling, i.e. dynamically decide what frequency should be used, "cpufreq governors" are usually set. In Linux kernel, there are five CPUfreq governors: conservative, ondemand, userspace, powersave, and performance. Powersave and performance set the CPU statically to the lowest and the highest frequency, respectively. The userspace governor allows the user to set the desired frequency. Ondemand and conservative dynamically change the frequency by sampling the CPU usage.

DVFS has a global effect on Sandy Bridge architecture, which means all the cores in the same CPU must run at an identical frequency. Newer architectures like Intel Haswell [46, 33, 47] and IBM Power8 [24] support separated voltage/frequency domains therefore DVFS can be applied to cores individually and cores can operate at different frequency levels.

#### 2.3.2 Duty Cycle Modulation

The hardware implementation of clock modulation involves setting the stopclock internal signal to regulate the CPU's normal "heartbeat". Intel Xeon Processors support software-controlled clock modulation. The stop-clock cycle is controlled through the IA32\_CLOCK\_MODULATION model specific register (MSR). By controlling the number of cycles to be skipped for every 16 clock cycles, various effective frequencies can be achieved.<sup>1</sup> For example, skipping eight cycles changes the effective frequency to be half the original. There are 16 available frequencies ranging from 6.25% to 100% of the maximum frequency, with a 6.25% interval. Once the "MSR" kernel module is loaded (via modprobe), users can write the desired value of IA32\_CLOCK\_MODULATION to the MSR device file (found under /dev/cpu/cpu\*/msr). Root privilege is required to control the power level as *modification* of MSR device files are protected. The Linux kernel has been locally modified to support a clock modulation system call. Changing the frequency via CPU clock modulation is a light-weighted process, requiring only a MSR write. The software controlled clock modulation can be applied on a core by core basis. The core-specific control provided by clock modulation

<sup>&</sup>lt;sup>1</sup> Our tested Intel Sandy Bridge architecture was enabled to support sixteen frequencies. In general, non-extended software controlled clock modulation supports eight frequencies, with an interval of 12.5%. Extension to software controlled clock modulation is supported only if CPUID.06H:EAX[Bit 5] = 1. Also the CPU must have ACPI feature to support both extended and non-extended software controlled clock modulation, i.e. CPUID.01H:EDX[Bit 22]=1.

allows for a much finer control over energy of an application. Modulating the CPU clock does not change the actual frequency or voltage and can be combined with DVFS. This permits an effective frequency well below the minimum DVFS frequency, providing more energy optimization options for applications. Table 2.1 shows the values to use to set the desired frequency.

| Duty Cycle Level | Binary | Decimal | Hexadecimal | Effective Frequency |

|------------------|--------|---------|-------------|---------------------|

| 1                | 10001B | 17      | 11H         | 6.25%               |

| 2                | 10010B | 18      | 12H         | 12.5%               |

| 3                | 10011B | 19      | 13H         | 18.75%              |

| 4                | 10100B | 20      | 14H         | 25%                 |

| 5                | 10101B | 21      | 15H         | 31.25%              |

| 6                | 10110B | 22      | 16H         | 37.5%               |

| 7                | 10011B | 23      | 17H         | 43.75%              |

| 8                | 11000B | 24      | 18H         | 50%                 |

| 9                | 11001B | 25      | 19H         | 56.25%              |

| 10               | 11010B | 26      | 1AH         | 63.5%               |

| 11               | 11011B | 27      | 1BH         | 69.75%              |

| 12               | 11100B | 28      | 1CH         | 75%                 |

| 13               | 11101B | 29      | 1DH         | 81.25%              |

| 14               | 11110B | 30      | 1EH         | 87.5%               |

| 15               | 11111B | 31      | 1FH         | 93.75%              |

| 16               | 00000B | 0       | 00H         | 100%                |

Table 2.1: Values to Write into IA32\_CLOCK\_MODULATION MSR to Achieve Duty Cycle Modulation.

In DVFS, the transition to lower frequencies takes much longer than clock modulation due to the overhead of switching between the supported Voltage/Frequency pairs using the on-chip voltage regulator. Energy savings are greater with DVFS (due to combined frequency and voltage reduction, the power dissipation of a CPU is proportional to the frequency and the voltage-squared) but the change of frequency overhead is much lower with clock modulation, requiring only a MSR write. By setting the clock modulation, no frequency and voltage transition must be involved, yet the effective frequency is reduced. This advantage makes it more suitable for fine-grained energy control of applications.

#### 2.3.3 Power Capping

Power Capping refers to putting a limit on the average power usage of the package. It is done by writing the power limit value into yet another RAPL MSR – MSR\_PKG\_RAPL\_POWER\_LIMIT. The power control is per package, i.e. over time the power consumption of the whole package is capped by the power limit.

#### 2.4 DVFS-Based Energy Saving Techniques

To optimize parallel applications for energy efficiency, the potential of DVFS has been extensively studied. One scenario of applying DVFS takes advantage of the work-load imbalance (slack) in MPI applications. Such systems include Jitter [41], Adagio [85], and Green Queue [99]. Kappiah et al., use a runtime system Jitter to predict the appropriate clock frequencies for upcoming iterations based on observations of previous iterations. In Adagio, Rountree et al., [85] present a runtime system that accurately predicts slack. Tiwari et al., [99], in Green Queue, combine inter-node DVFS approach and intra-node DVFS approach and scale the DVFS technique to 1024 cores. The CPU clock modulation technique discussed should be applicable to all this related work.

Another common use of DVFS is to divide applications into phases first and then apply appropriate DVFS setting to each phase. Freeh et al., [26] choose different frequency settings according to application profile to be applied to different MPI phases. The MPI application is executed using multiple energy "gears" to realize energy savings. Livingston et al. [51] present REST to dynamically detect the memory intensive and compute intensive phases of MPI applications. Machine frequency is changed via DVFS. Other work utilizes performance counters [50, 28] to build power/energy models and use these built models to predict the optimal frequency setting for an application. In this dissertation, a simple memory access related counter is used to categorize OpenMP loops. Different energy settings were applied in fine granularity using the clock modulation technique. Other DVFS use cases include combining concurrency throttling to optimize for energy on multi-core platforms [19]. In contrast, concurrency throttling is combined with clock modulation to realize energy savings in this work. Eyerman et al., studied the potential of fine-grain DVFS in saving energy for memory-intensive applications [22]. In absence of the hardware that supports fine-grained DVFS, our work favors software clock modulation over DVFS.

## 2.5 Clock-Modulation-Based Energy Saving Techniques

While DVFS has been extensively studied, only a handful of work (including our previous work [104]) has looked at employing clock modulation techniques to save application energy. Sundrival et al., [96] apply clock modulation in inter-node communication phases of MPI applications to achieve significant energy savings with low overhead. They also apply the same technique in point-to-point communications [94] and collective communications [95]. Cicotti et al., [17] present Efficient Speed (ES), a library and run-time that controls the speed of processor while minimizing the performance impact. They achieved 16% energy decrease with less than 5% performance loss for MPI applications. We present an equivalent infrastructure for power measurement and control targeting OpenMP applications that achieves 10% energy savings with less than 1% performance loss for many kernels. In other energy optimization work [110], clock modulation techniques have been used to realize resource utilization management on servers.

### 2.6 Concurrency Throttling

Concurrency throttling is a software mechanism to modulate the amount of concurrency for regulating application runtime performance on systems with multi-core processors. By reducing the number of threads used for executing the applications, the concurrency level is regulated. This technique was used with DVFS for predicting the best configuration setting, i.e., the frequency and concurrency level, on HPC systems [19]. It has also been applied to realize energy savings for OpenMP benchmarks, such as LULESH and BOTS [76]. In that work, Porterfield et al., developed a run time system that automatically adjusted the concurrency level based on hardware performance counters, achieving energy reductions without performance lost. In this dissertation, we combine clock modulation with concurrency throttling to achieve even more energy/EDP improvements. Li et al., combined DVFS with dynamic concurrency throttling (DCT) to achieve improved EDP in hybrid (OpenMP/MPI) programming models [49]. In that work, they presented models and algorithms for energy efficient execution of hybrid MPI/OpenMP applications. After characterizing energy-saving opportunities in these hybrid applications, they applied DCT and DVFS to leverage these energy-saving opportunities without performance loss. In this dissertation, we focus on applying concurrency throttling techniques with power saving techniques for OpenMP applications on different architectures, including the Intel Sandy Bridge architecture (with CPU clock modulation) and the IBM Power8 architecture (with DVFS).

#### 2.7 Existing Performance-Energy Correlation Studies