# MEMORY OPTIMIZATION IN CODELET EXECUTION MODEL ON MANY-CORE ARCHITECTURES

by

Yao Wu

A thesis submitted to the Faculty of the University of Delaware in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Computer Engineering

Spring 2014

© 2014 Yao Wu All Rights Reserved UMI Number: 1562437

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### UMI 1562437

Published by ProQuest LLC (2014). Copyright in the Dissertation held by the Author.

Microform Edition © ProQuest LLC.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 - 1346

##

by

## Yao Wu

| Approved:  |                                                                   |

|------------|-------------------------------------------------------------------|

| 11pproved. | Guang R. Gao, Ph.D.                                               |

|            | Professor in charge of thesis on behalf of the Advisory Committee |

|            |                                                                   |

|            |                                                                   |

| Approved:  |                                                                   |

|            | Kenneth E. Barner, Ph.D.                                          |

|            | Chair of the Department of Electrical and Computer Engineering    |

|            |                                                                   |

|            |                                                                   |

| Approved:  |                                                                   |

|            | Babatunde A. Ogunnaike, Ph.D.                                     |

|            | Dean of the College of Engineering                                |

|            |                                                                   |

|            |                                                                   |

| Approved:  |                                                                   |

|            | James G. Richards, Ph.D.                                          |

|            | Vice Provost for Graduate and Professional Education              |

#### ACKNOWLEDGMENTS

First of all, I want to express my deep gratitude to my advisor Prof. Guang R. Gao who guided and support in my research. His research attitude and enthusiasm have influenced me greatly. Under his guidance, I gained a lot of knowledge and skills. The experiences in CAPSL will benefit me for my future life.

I would like to acknowledge Dr. Chen Chen and Dr. Long Zheng who are my mentors and gave great help on my research. Dr. Chen Chen introduced OpenMP, SWARM, Cyclops-64 and parallel coding skills to me. I learned Hadoop and Java coding from Dr. Long Zheng. He provided feedback to revise my thesis. I can not accomplish my thesis without their help.

I also want to thank all CAPSL members who taught and helped me during my study.

Finally, I would like to give thanks to my parents, wife, and son. They always supported my work, understood me and gave me great patience.

This work is supported by the Department of Energy [Office of Science] under Award Number DE-SC0008717.

This work is partially supported by European FP7 project TERAFLUX, id. 249013.

## TABLE OF CONTENTS

| LI<br>LI     | ST (                     | OF FIG<br>OF AL                           | BLES                                       | vii<br>vii<br>ix<br>x      |

|--------------|--------------------------|-------------------------------------------|--------------------------------------------|----------------------------|

| $\mathbf{C}$ | hapte                    | $\mathbf{er}$                             |                                            |                            |

| 1            | INT                      | RODU                                      | UCITON                                     | 1                          |

| 2            | BA                       | CKGR                                      | OUND                                       | 5                          |

|              | 2.1<br>2.2<br>2.3<br>2.4 | The C<br>Impler                           | iew of Multi- and Many-core Systems        | 5<br>6<br>8<br>10          |

| 3            | ME                       | MORY                                      | WORKLOAD BALANCE IN CODELET PXM            | 14                         |

|              | 3.1                      | Metho                                     | odology                                    | 14                         |

|              |                          | 3.1.1<br>3.1.2<br>3.1.3                   | Motivating Example                         | 14<br>16<br>21             |

|              | 3.2                      | Experi                                    | iment                                      | 21                         |

|              |                          | 3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5 | Task Size and Theoretical Peak Performance | 21<br>24<br>25<br>26<br>26 |

|              | 3.3                      | Relate                                    | ed Work                                    | 27<br>30                   |

| 4 | LO   | CALIT  | TY EXPLOITATION IN CODELET PXM     | 33        |

|---|------|--------|------------------------------------|-----------|

|   | 4.1  | Metho  | odology                            | 33        |

|   |      | 4.1.1  | Motivating Example                 | 33        |

|   |      | 4.1.2  | Problem Statement                  | 36        |

|   |      | 4.1.3  | Solution                           | 37        |

|   | 4.2  | Algori | ithm                               | 37        |

|   |      | 4.2.1  | Min-cost Flow Based Algorithm      | 38        |

|   |      | 4.2.2  | Max First Algorithm                | 40        |

|   |      | 4.2.3  | Graph Partitioning Based Algorithm | 42        |

|   | 4.3  | Exper  | iment                              | 43        |

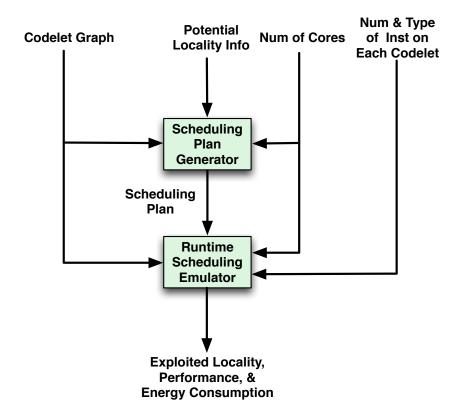

|   |      | 4.3.1  | Experimental Design                | 43        |

|   |      | 4.3.2  | Major Observations                 | 47        |

|   |      | 4.3.3  | Experimental Result                | 47        |

|   | 4.4  | Relate | ed Work                            | 52        |

|   | 4.5  | Discus | ssion                              | 54        |

| 5 | CO   | NCLU   | SION AND FUTURE WORK               | <b>56</b> |

| B | IBLI | OGRA   | APHY                               | <b>58</b> |

## LIST OF TABLES

| 3.1 | Description of the various methods used to perform FFT on Cyclops-64           | 24 |

|-----|--------------------------------------------------------------------------------|----|

| 4.1 | The description of the four algorithms used to schedule codelets on Cyclops-64 | 46 |

| 4.2 | Energy consumption per instruction                                             | 49 |

## LIST OF FIGURES

| 2.1 | The Cyclops-64 node block-diagram                                                                                                           | 7  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | The Cyclops-64 memory hierarchy                                                                                                             | 8  |

| 2.3 | An 8-point FFT butterfly                                                                                                                    | g  |

| 2.4 | Abstract machine for the codelet model                                                                                                      | 13 |

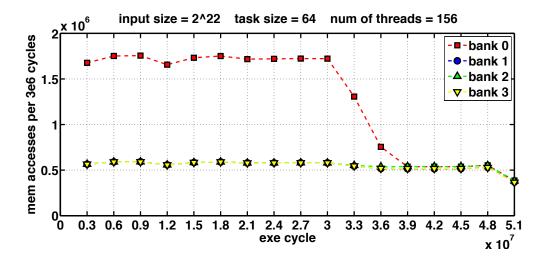

| 3.1 | Access rates of the 4 off-chip memory banks in the coarse-grain FFT algorithm                                                               | 15 |

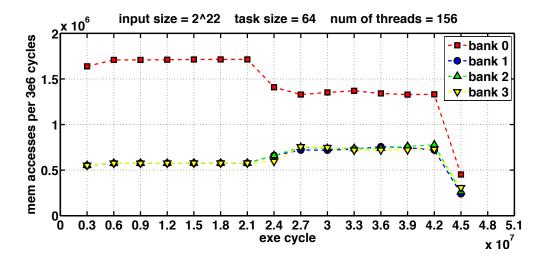

| 3.2 | Access rates of the 4 off-chip memory banks in the fine-grain FFT algorithm                                                                 | 16 |

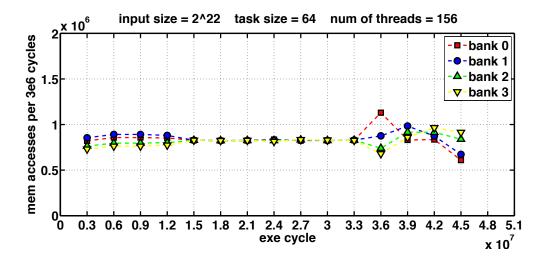

| 3.3 | Access rates of the 4 off-chip memory banks in the fine-grain FFT algorithm with randomized twiddle factor addresses                        | 22 |

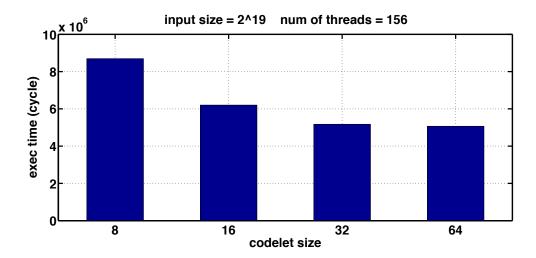

| 3.4 | The best execution time of the fine-grain FFT algorithm for 156 threads units running in parallel and a global input data set of $2^{19}$ . | 23 |

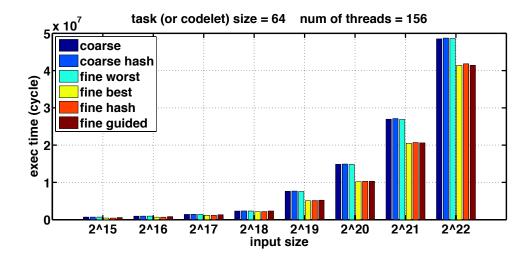

| 3.5 | The execution time of 5 versions of FFT algorithms on Cyclops-64.                                                                           | 25 |

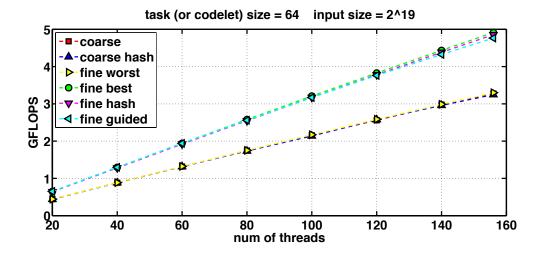

| 3.6 | Performance of 5 versions of FFT algorithms on Cyclops-64 for an input size of $2^{19}$ data elements and 64-point butterfly codelets       | 27 |

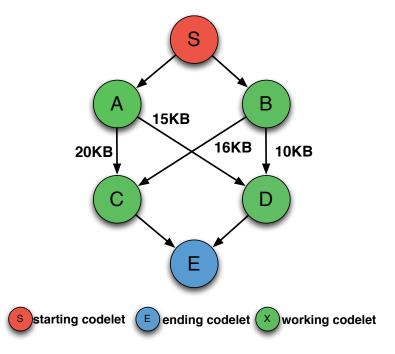

| 4.1 | A motivating example of locality exploitation in the codelet model.                                                                         | 34 |

| 4.2 | A simplified SWARM codelet program corresponding to the codelet graph in Figure 4.1                                                         | 35 |

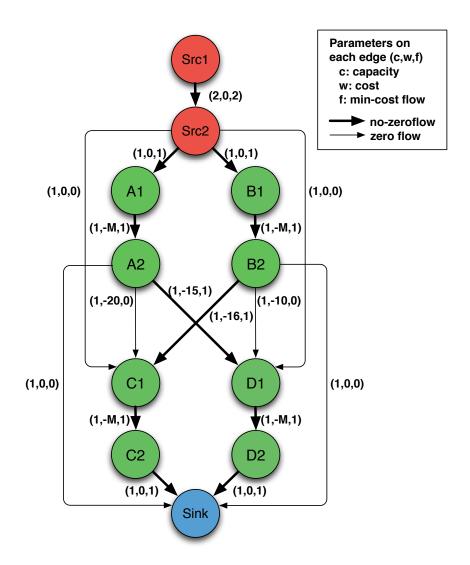

| 4.3 | The flow network converted from the codelet graph in figure $4.1.$ .                                                                        | 39 |

| 4.4 | Experiment design                                                                                                                           | 44 |

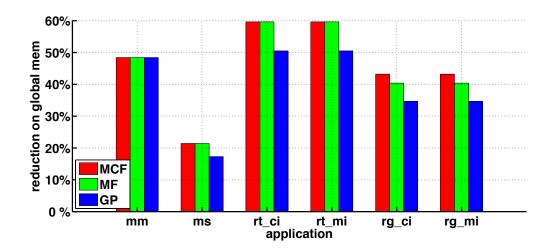

| 4.5 | The best locality exploitation on the six applications by using the three algorithms from Section 4.2 | 48 |

|-----|-------------------------------------------------------------------------------------------------------|----|

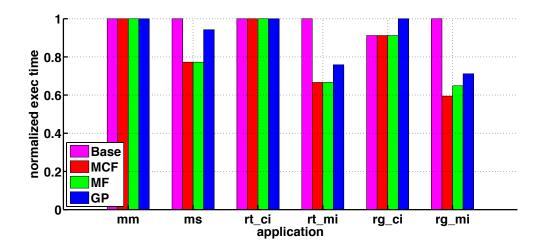

| 4.6 | The performance of the four algorithms on the six applications                                        | 50 |

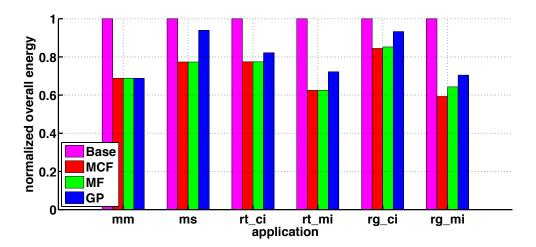

| 4.7 | The overall energy consumption of the six applications by using the four algorithms                   | 51 |

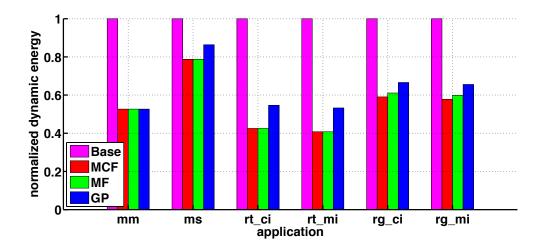

| 4.8 | The dynamic energy consumption of the six applications by using the four algorithms                   | 52 |

## LIST OF ALGORITHMS

| 1 | The pseudo code of the coarse-grain 64-point FFT algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 17 |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2 | The pseudo code of the fine-grain 64-point FFT algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 19 |

| 3 | The pseudo code of the guided fine-grain 64-Point FFT algorithm $% \left( 1\right) =\left( 1\right) +\left( 1\right) +\left($ | 32 |

| 4 | Using min-cost flow to solve the Best Scheduling Problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 41 |

| 5 | Max first algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 42 |

#### ABSTRACT

The upcoming exa-scale era requires a parallel program execution model capable of achieving scalability, productivity, energy efficiency, and resiliency. The codelet model is a fine-grained dataflow-inspired execution model which is the focus of several tera-scale and exa-scale studies such as DARPA's UHPC, DOE's X-Stack, and the European TERAFLUX projects.

Current codelet implementations aim to making fully use of computation resources by balancing their workload in the multi-core and many-core systems. The performance is improved by this method. However, by making use of the features of the codelet model the memory optimization can be also implemented to improve the performance as well as energy efficiency. In this thesis, we focus on the memory optimization on memory workload balance and locality exploitation in the codelet model. As a case study, various versions of FFT algorithms are implemented on IBM Cyclops-64 – a many-core system to demonstrate that the fine-grain codelet execution model is able to execute the codelets that involve different workload on the memory bandwidth in an appropriate order to reduce memory contention and thus improve performance. The experiment result shows that our fine-grain guided algorithm achieves up to 46% performance improvement comparing to a coarse-grain implementation on Cyclops-64. To automatically exploit locality in codelet execution, we provide three optimal or nearly optimal scheduling algorithms based on static information of codelet graph and locality. They have different trade-offs in algorithmic complexity, locality exploitation, program execution time, and energy efficiency. We test and analyze the three algorithms on various applications on an emulation platform of Cyclops-64. The experiment result shows that our algorithms reduce up to 59.7% of global memory access by using local memory to buffer intermediate data between two adjacent codelets on the same core and thus improve up to 68.1% performance improvement and 40.7% energy saving comparing to the dynamic codelet scheduling approach.

#### Chapter 1

#### INTRODUCITON

To achieve better performance, more and more cores are integrated into systems. Multi-core and many-core systems are becoming popular and many have been available on market [2, 6, 67, 20, 27, 65, 60]. Therefore, the approaches to effectively utilizing these systems draw considerable attention. Conventionally, parallel execution in multi-core and many-core systems is based on coarse-grain synchronization by using barriers e.g. MPI and OpenMP that are the most prevailing parallel programming models today. These coarse-grain models perform well on a system where the number of cores is small, but tend to degrade as the core count increases [38, 58]. The reason is that the contention for shared resources e.g. shared memory and floating-point units becomes severer among cores as the number of cores increases.

For this reason, different execution models are required to achieve high-performance computing for multi-core and many-core systems. The codelet model is designed to realize fine-grain parallel execution for extreme-scale machines. This model is originated from dataflow and also takes advantage of the Von Neumann model. In the codelet model, the programs can be expressed by codelets and the dependencies among them. Runtimes based on codelet execution model are able to schedule ready codelets to run on available resources. Comparing to the coarse-grain model, the asynchronously event-driven execution in the codelet model can achieve more balanced workload on computation.

Moreover, by making use of the features of the codelet model the memory optimization can be implemented to improve the performance as well as energy saving in the mutli-core and many-core systems. In this thesis, we focus on the memory optimization on memory workload balance and locality exploitation in the codelet execution model.

In this thesis, we show that the fine-grain codelet execution model can achieve more balanced workload on not only computation but also memory bandwidth than the coarse-grain execution model can. The codelet execution model provide an opportunity to control the order of the codelet execution. Because each codelet maybe has different memory access patterns, the execution order can be controlled to provide a evenly distributed access pattern among memory banks such that the system achieves better workload balance on the memory bandwidth usage. We use FFT algorithm on the IBM Cyclops-64 many-core architecture to demonstrate the advantage of the fine-grain execution model by using codelet model.

Although the codelet model is able to exploit parallelism effectively to improve workload balance, data locality is not well considered when scheduling codelet. In some multi-core and many-core systems, system memory is organized hierarchically by globally shared memory among cores and local memory for each core e.g. IBM Cyclops-64 [21], IBM CELL Broadband Engine [1], and Intel UHPC straw-man [48]. Globally shared memory e.g. interleaved SRAM and DRAM are used to share data and communicate/synchronize among cores. Local memory e.q. scratchpad SRAM is used to store the data for further reuse. The access latency and energy consumption of local memory is much lower than that of shared global memory. For such systems, locality exploitation is very important, because it achieves better performance and more efficient energy consumption. The conventional method to exploit data locality highly relies on programmers to manually generate the scheduling plan. This process is extremely time-consuming. In this thesis, our effort is to introduce a automatic mechanism to guide codelet runtimes in exploiting locality by using the codelet graph and locality information. This automatic approach can exploit best data locality as well as keep the highest parallelism in programs by using static scheduling in codelet runtimes.

The major contributions of this thesis are as follows:

- A fine-grain FFT algorithm based on codelet model is designed and implemented on the IBM Cyclops-64 many-core architecture. With a heuristic order guiding the execution of the codelets, the memory contention is reduced.

- The behavior of three versions of FFT on different granularity of synchronization are compared: coarse-grain (using barriers), fine-grain (using point-to-point synchronization), and guided fine-grain (fine-grain with the heuristic guidance). The experiment result shows that our algorithm achieves up to 46% performance improvement comparing to the coarse implementation on Cyclops-64.

- The fine-grain approach with an alternative solution that reduces memory contention by randomizing memory addresses is implemented and compared. The fine-grain approach outperforms the address randomization approach when the input data size is large enough. Moreover, the performance gap will enlarge as the input data size increases.

- A polynomial-time algorithm is proposed to statically scheduling codelets to achieve best data locality while keeping the highest parallelism when there are enough computation resources. The least computation resource requirement for running parallel programs is also guaranteed by the algorithm.

- Other two widely used algorithms are analyzed and implemented to make a comparison. These three algorithms have different trade-offs in algorithmic complexity, locality exploitation, program execution time, and energy efficiency. Theoretically and experimentally, our algorithm provides the best performance as well as the most efficient energy consumption.

- These three algorithms are tested and analyzed on various applications including matrix multiply, merge sort, and random generated codelet graphs with reasonable assumptions. The experimental results show that our algorithm can reduce up to 59.7% of global memory access by optimizing locality exploitation. Our algorithm also improves up to 68.1% performance improvement and 40.7% energy saving comparing to the dynamic codelet scheduling.

Our work described above has been published in the international conference and workshop. In particular, this thesis is also based on the published papers [14, 12, 13].

The rest of the thesis is organized as follows. Chapter 2 provides the background on the architecture, execution model, and FFT algorithm of our work in this thesis. Chapter 3 demonstrates the memory workload balance optimization in the codelet model by using FFT algorithm. Chapter 4 introduces the memory locality exploitation

optimization in the codelet model by comparing different scheduling algorithms on various applications. Chapter 5 gives the conclusion and future work of our work.

#### Chapter 2

#### **BACKGROUND**

In this chapter, we introduce the evolution of multi- and many-core systems in Section 2.1, the IBM Cyclops-64 many-core architecture that is used as the experimental platform in Section 2.2, the previous work on the FFT algorithm on Cyclops-64 in Section 2.3, and the codelet model by which we implement various fine-grain algorithms in Section 2.4.

#### 2.1 Overview of Multi- and Many-core Systems

As the requirements for computation are drastically increasing, the manufacturers achieve the microprocessor performance mainly in two ways. One is based on the frequency boost of a microprocessor, so that more cycles are in one second *i.e.* more instructions can be executed in a second. On the other hand, as more transistor can be integrated into a microprocessor (since a transistor is getting smaller and smaller), Instruction Level Parallelism (ILP) is achieved to execute more instructions in a cycle. Therefore, both approaches improve the performance of microprocessors. Instruction Level Parallelism has been widely studied over many years, such as super scale, out-of-order execution, long pipeline, multi-issue, branch prediction, and speculation. However, high clock frequency brings in thermal problem and small transistor tends to reach its physical limit. Therefore, the two methods are not suitable for performance enhancement any more.

Recently, the microprocessor industry is tending toward multi-core and many-core. It is an easier and more efficient way to improve the performance of microprocessors by integrating more cores into a chip. Many multi-core and many-core architectures are designed to demonstrate the significant computation power. The CELL

Broadband Engine [1] processor is a heterogeneous multi-core microprocessor which provides powerful graphics processing performance. It consists of a Power Processor Element (PPE) which controls eight SIMD Synergistic Processor Element (SPE). IBM Cyclops-64 [21] (see Section 2.2) contains 80 processors each of which has two thread units. Intel UHPC straw-man [48] architecture is composed of three levels: chip, cluster, and block. A chip consists of a group of clusters. A cluster contains many blocks. In a block, there are N execution engines (XE) and one control engine (CE). Network processors contain tens of thousands of cores to enhance and optimize packet processing in the networks [4]. GPU is widely used in graphics processing as well as supports the general-purpose computation [44]. Nowadays, it can contain up to thousands of cores. Different architectures involve different hardware features which can be taken advantage to optimize specific computations. After the microprocessors evolve into multi-core and many-core, not only Instruction Level Parallelism but also Thread Level Parallelism (TLP) are used to enhance the performance. The difference between multi-core and many-core is the number of cores integrated in a chip. In general, multi-core refers to the systems with eight or less cores, such as most of the Intel x86 CPUs with a small number of cores. Many-core refers to the systems with more than eight cores, such as Cyclops-64, Intel straw-man, and GPU. Nowadays, multi-core and many-core are becoming the mainstream in computer systems. However, it also brings in challenges to effectively make use of their computation power as well as improve energy efficiency.

In this thesis, we focus on both performance and energy optimization on multicore and many-core architectures by using fine-grain codelet execution model (see Section 2.4) instead of the conventional coarse-grain approaches, such as MPI and OpenMP.

#### 2.2 The Cyclops-64 Architecture

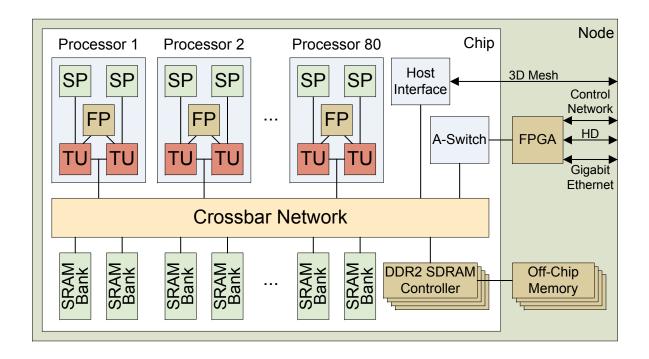

Figure 2.1 shows a block-diagram of a Cyclops-64 node. Each node runs at 500 MHz and contains 80 processors. Each processor contains 2 thread units (TU)

**Figure 2.1:** The Cyclops-64 node block-diagram. A node has 80 processors each of which contains 2 thread units (TU), a floating-point unit (FP), and local scratchpad SRAM (SP). All processors access global SRAM and off-chip DRAM through the crossbar network.

which share a floating-point unit (FP). A thread unit is an in-order 64-bit RISC core with a register file composed of 64 64-bit registers. It does not support for context switch, so each TU only runs one thread. Each FP is able to issue one fused multiply-add instruction (FMA) per cycle. Hence, the theoretical peak performance of a Cyclops-64 node is a 80 GFLOPS.

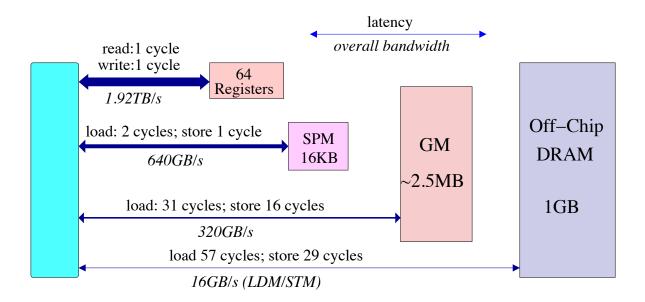

As shown in Figure 2.2, Cyclops-64 has a three layer memory hierarchy without data cache: scratchpad SRAM, interleaved SRAM, and DRAM which are accessed by all TUs through a 96-port crossbar switch. A Cyclops-64 node is equipped with about 5 MB on-chip memory SRAM, which is divided into 160 memory banks of 30 KB each. By default, these banks are equally split into interleaved (global) SRAM which can be accessed by all TUs and scratchpad (local) SRAM which is local to and can be accessed much faster by the corresponding TU). Note that the amount of global SRAM

**Figure 2.2:** The Cyclops-64 memory hierarchy. A node has a three layer memory hierarchy without data cache: scratchpad SRAM, interleaved SRAM, and off-chip DRAM. Each layer has different memory bandwidth and access latency.

and scratchpad memory can be configured at boot time. The bandwidth to access interleaved and scratchpad SRAM are 320 GB/s and 640 GB/s respectively. There is 1 GB off-chip DRAM memory on a Cyclops-64 node. Off-chip DRAM accesses are significantly slower from 16 GB/s for multiple-load / multiple-store instructions down to 2 GB/s for sequences of single-load or single-store instructions. Off-chip memory is only accessed through 4 banks. Workload imbalance on DRAM ports on Cyclops-64 becomes serious if the data does not distribute evenly on each bank. In this case, some ports are so busy that causes contentions and access delay while others are free. Our work shows that the codelet model provides the possibility to balance DRAM access pattern to achieve better performance.

#### 2.3 Implementation of FFT on Cyclops-64

Fast Fourier Transform (FFT) is a very useful algorithm in signal processing area. Many different implementations of FFT on different architectures have been

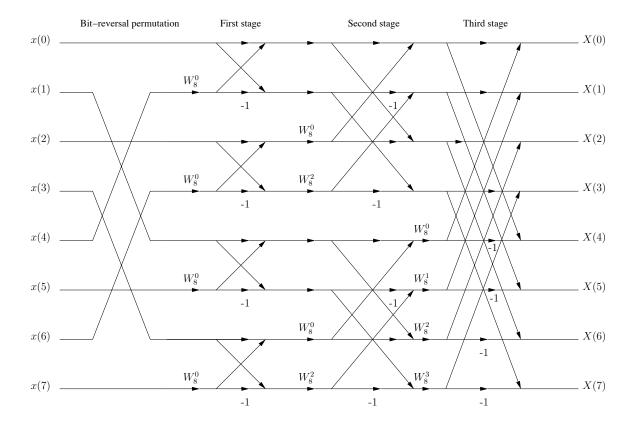

**Figure 2.3:** An 8-point FFT butterfly, as demonstrated by Chen *et al.* [15]. Such a task can be executed on a thread independently in 3 stages butterfly operations *i.e.* without communication or data exchange with other tasks.

widely studied over the years. One of which, FFTW, is still considered among the most efficient on multi-core and many-core systems. However, most of these parallel implementations still take advantage of coarse-grain synchronization between cores. There are only a few FFT studies driven by fine-grain execution models to achieve better balanced workload on computation.

Chen et al. [15] demonstrated the implementation of 1D and 2D FFT algorithm on Cyclops-64. Their method implemented the classical Cooley-Tukey algorithm in an iterative instead of recursive way. The cores are synchronized by using the hardware barrier provided by Cyclops-64 at the end of multiple stages which depends on the size of butterfly computation *i.e.* task size. They only used SRAM and the register files

in FFT computation. As shown in Figure 2.3, 2-point butterfly in original Cooley-Tukey algorithm was extended to 8-point butterfly. There is additional step i.e. bit reversal permutation before all butterfly operations. It is used to change the input data positions to guarantee the output data in correct positions. If we don't apply such a step before the butterfly computation, we can also involve it at end of the butterfly computation to achieve the same effect. Such a step must be executed once and only once in FFT implementation. They divided the whole computation into many small parallel tasks which load the data the pre-computed twiddle factors from SRAM to registers, apply butterfly computation, and store the intermediate or final results back to SRAM in place [15]. Figure 2.3 shows a task whose input is 8 data points. Accord to the feature of FFT algorithm, such a task can be executed on a thread independently in 3 stages butterfly operations i.e. without communication or data exchange with other tasks. We can see that as the task size increases the data exchange between SRAM and registers reduces. It keeps cores busy for computation for a longer time. Furthermore, it also makes the whole computation need less barriers. However, too large task size hurts the parallelism and can not be implemented in their work because the number of register on each core is limited on Cyclops-64. They stored all the data are stored in the on-chip SRAM memory and found that when the task size is set as an 8-point butterfly, the performance is the best.

However, because of the limited size, on-chip memory can not be fitted in for a large input data size. Hence, we need to extend on-chip to off-chip memory data storage and use scratchpad instead of registers for intermediate data. In this case, we found that 64-point FFT performs better than the 8-point FFT due to the reduction of off-chip memory accesses.

#### 2.4 The Codelet Model

Our work is based on the codelet program execution model [75, 34]. The feature of the codelet model provides us a chance to improve the performance and reduce energy computation during parallel execution.

The codelet model takes both advantages of dataflow and Von Neumann models [25]. It is a hierarchical fine-grain multithreading model that are based on the concepts and semantics of codelets. According to the parallelism and data dependencies, the programs are divided and capsulated into codelets *i.e.* a collection of instructions. The codelet is the finest granularity of parallelism in the model. Inside a codelet, the instructions are executed sequentially. A codelet run asynchronously without blocking until it completes. Usually, a codelet runtime is involved to schedule each codelet to the computation unit by the scheduling rules. Since codelets have a larger granularity than instructions, it provides an opportunity to reduce runtime overhead by tuning the size of codelet. Codelet execution is event-driven which means only when the required data and resources are available, the codelets receive all synchronized signal and can start execution.

Each codelet can have one of the following 4 status:

- Dormant: Not yet receive all required data.

- Enabled: Receive all the data required to execute the codelet.

- Ready: Enabled and all resources needed to execute the codelet are ready.

- Firing: Execution of a ready codelet when it is scheduled on a processing unit.

A codelet changes among the 4 status according to availability of data and computation resources.

According to data dependencies, the codelets in a program are connected together into a graph called the codelet graph (CDG) which has its root in dataflow graph [25]. If a codelet graph is well-behaved e.g. no deadlock caused by a cycle in the codelet graph, the execution will be determinate i.e. the outputs always are the same for a given input to the codelet graph. However, the execution order of codelets in each run is not guaranteed to be the same, because the occurrence of the events to trigger the codelets highly depends on runtime and hardware system. Our work in fine-grain FFT algorithm makes use of the changeable execution order of codelets to improve the memory bandwidth usage.

In general, the whole codelet graph is not required to statically construct. It is started by setting up a part of codelets and their dependencies statically and then the other subgraphs can be created dynamically by the running codelets. Our fine-grain FFT algorithms produce the codelet graph at the beginning of the execution when the input data size is known. Our work in locality exploitation in the codelet model also takes advantage of a purely static codelet graph.

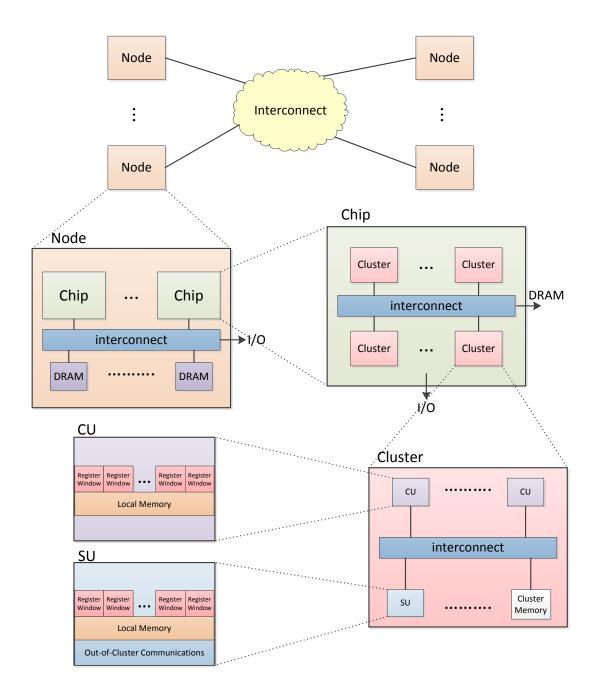

The codelet model can be mapped to corresponding abstract parallel computer hardware and software system called abstract machine. As shown in Figure 2.4, the codelet abstract machine is organized hierarchically with heterogeneous elements. It consists of many nodes which are linked together by an interconnection network. Each node has one or more many-core chips and shared node memory. Each chip contains many clusters connected together by a chip interconnect and shared chip memory. Each cluster contains a collection of computing units (CU) and one or more synchronization and scheduling units (SU) which are linked together by an on-chip interconnect and share cluster memory. Computing units, which can be any type of core, are in charge of computation i.e. executing codelets. Synchronization units are responsible for scheduling the codelets to available computing units based on the scheduling rules to achieve performance and energy saving. Synchronization units also handle exceptions, hardware interruption, memory request from or to out-of-cluster location, etc. Each computing unit or synchronization unit has its own local memory. The hierarchical feature of the codelet abstract machine can improve locality in programs by organizing the codelets into specific levels of the machine.

Figure 2.4: Abstract machine for the codelet model. It is organized hierarchically with heterogeneous elements. At cluster level, computing units (CU) execute ready codelets and synchronization units (SU) schedule the codelets to available computing units. There is share memory at each level to achieve the locality.

#### Chapter 3

#### MEMORY WORKLOAD BALANCE IN CODELET PXM

In this chapter, we demonstrate that the fine-grain execution models can improve more balanced workload on not only computation but also memory bandwidth usage than the coarse-grain execution models can. We implement FFT algorithm on the IBM Cyclops-64 many-core architecture to show the advantage of the fine-grain execution model by using codelet model. The related work is also provided.

#### 3.1 Methodology

This section introduces and analyzes the methodology of our work. Section 3.1.1 uses an example to demonstrate the opportunity provided by the codelet model to improve the memory bandwidth usage. Section 3.1.2 describes coarse-grain, fine-grain, and guided fine-grain FFT algorithms with 64-point task size. Section 3.1.3 presents our way to randomize the off-chip memory addresses in order to achieve balanced memory bandwidth usage.

#### 3.1.1 Motivating Example

We have described the coarse-grain FFT algorithm on Cyclops-64 in Section 2.3. This algorithm shows very good performance when using on-chip memory [15]. However, when we extend this algorithm to using off-chip memory to store the data and twiddle factors, it does not work well. We found that the problem is caused by the unbalanced memory accesses to the off-chip memory banks.

As described in Section 2.2, there are only 4 ports connecting 4 off-chip memory banks respectively on a Cyclops-64 node. From Figure 3.1, we can see that the memory accesses only in the last few stages (about last 1/3 of the execution time) are evenly

**Figure 3.1:** Access rates of the 4 off-chip memory banks in the coarse-grain FFT algorithm. In early stages,  $Bank \ \theta$  is accessed three times more than the other banks. It causes contention on  $Bank \ \theta$  and wastes the bandwidth resource on other banks.

distributed to the four memory banks in the coarse-grain FFT algorithm. In early stages (about first 2/3 of the execution time),  $Bank \ \theta$  is accessed three times more than the other banks. It causes contention on  $Bank \ \theta$  and wastes the bandwidth resource on other banks. Because the accessed elements in the twiddle factor array in early stages have a stride that is a multiple of 64 in the memory address and the four off-chip memory banks are interleaved on 64-byte boundaries as well (In a Cyclops-64 node, the first 64 bytes of data are stored on  $bank \ \theta$ ), the next 64 bytes on  $bank \ 1$ , and so on so forth.), the accesses on the twiddle factor array in early stages always go to  $bank \ \theta$ . However, because the stride of the accessed addresses in the last few stages is less than 64, the access rates of the four memory banks are more balanced.

In fine-grain execution models, it is possible for a task in a later stage to be executed prior to a task in an early stage. Therefore, the execution order of the tasks can be guided to get more balanced workload on the memory banks. Some tasks in early stages which only need the data on  $bank \ \theta$  can be delayed execution in order to relieve the burden on  $bank \ \theta$ . On the other hand, some tasks in late stages which

**Figure 3.2:** Access rates of the 4 off-chip memory banks in the fine-grain FFT algorithm. Compared to Figure 3.1, the memory access pattern is much more balanced starting from the second half of the execution time. Contention reduces on  $Bank \ \theta$  and the bandwidth resource on other banks can be made use of earlier.

need the data on bank 1, 2, 3 can be advanced to execute so that the bandwidth of bank 1, 2, 3 can be made use of when free. Figure 3.2 demonstrates the access pattern of the off-chip memory banks in our designed fine-grain FFT algorithm. We can see that the access pattern is more balanced by the access rate of bank 0/bank 1, 2, 3 decreasing/increasing earlier (at about 1/2 of the execution time).

An alternative solution to balance the memory access workload is to randomize the memory addresses of the elements in the twiddle factor array. However, the software method of randomizing the memory addresses introduces big overhead. On the other hand, the feature of randomizing the memory addresses by hardware is not supported by all architectures, because such a feature breaks locality for regular applications. For comparison, we also implement FFT algorithm with hashed twiddle factor array.

#### 3.1.2 Three FFT Implementations

#### Coarse-Grain Algorithm

Algorithm 1 The pseudo code of the coarse-grain 64-point FFT algorithm

```

input: Array D with input data

Array W with pre-computed twiddle factors

output: Array D with final results

PSEUDO CODE:

Bit\_reversal(D) in parallel;

N \leftarrow D.length;

last\_stage \leftarrow \lceil log_2 N/6 \rceil - 1;

for stage = 0 to last\_stage do

if stage \neq last\_stage then

for t_{-}id = 0 to N/64 - 1 in parallel do

FFT_64p_kernel(D,W,stage,t_id);

end for

else

for t_{-}id = 0 to N/64 - 1 in parallel do

FFT_last\_stage\_kernel(D,W,stage,t\_id);

end for

end if

barrier;

end for

```

The 64-point FFT coarse-grain algorithm can be viewed as an extension of Chen et al.'s 8-point FFT algorithm that is described in Section 2.3.

The pseudo code of the coarse-grain 64-point FFT algorithm is shown in Algorithm 1. As other Cooley-Tukey based FFT algorithms, the parallel bit-reversal process before butterfly computations is required to change the input data position to guarantee the output data in correct positions. Then, the whole FFT computation is divided into  $\lceil log_2N/6 \rceil$  stages, where N is the number of the input data. Without loss of generality, we assume that N is a power of two because in FFT algorithm we always append amount of zero data to make the input data size as a power of two. In each stage, there are N/64 tasks. Each task is a 64-point FFT kernel that loads 64 data points and 63 twiddle factors from the off-chip memory to scratchpad, applies butterfly computation on 6 levels (the intermediate data are stored in scratchpad), and stores 64 computed data back to the off-chip memory in place. At the end of each stage, all the threads are synchronized by a barrier. Tasks in the last stage may apply less than 6 levels of butterfly computation because  $log_2N$  may not be a multiple of 6. In such a

case, tasks in the last stage only applies  $log_2N \mod 6$  levels of butterfly computation.

Each task loads 64 data in the following way: Suppose that the task is the *i*th one in stage j. The thread loads  $data_0,...,data_{63}$  from the data array D where

$$data_k = D[64^{j+1} \times |i/64^j| + i \mod 64^j + k \times 64^j]$$

Moreover, the task also loads twiddle factors for each level of the FFT computation. At level l, the mth butterfly computation needs the twiddle factor

$$\omega_{lm} = W[m \bmod 2^l \times 2^{log_2N - l - 1}]$$

#### Fine-Grain Algorithm

We can see that each task only needs 64 data and 63 pre-computed twiddle factors as input in the coarse-grain FFT algorithm,. The 64 inputs are generated by the output of the 64 parent tasks in the previous stage. For example, a task in  $stage\ 1$  can execute once its 64 parent tasks in  $stage\ 0$  have completed. It provides an chance to remove the barriers in the coarse-grain FFT algorithm. Therefore, we propose the fine-grain FFT algorithm as shown in Algorithm 2.

The codelet model is used to represent the fine-grain FFT algorithm. Each task in the coarse-grain FFT algorithm is a codelet in the fine-grain FFT algorithm. If the total number of codelets are much more than the total number of threads, the computation workload is balanced. A counter is associated with a codelet instead of using a barrier to achieve the synchronization by updating the number of satisfied dependencies. A concurrent codelet pool is used to store all the codelets that are ready to be executed *i.e.* all the dependencies are satisfied. Initially, all the codelets in stage  $\theta$  are put in the pool since their input data are already available. During the execution, once a thread completes a codelet, it will increase the dependency counters of all the children of the codelet. The child codelet that reaches 64 on its counter becomes ready and will be put into the codelet pool. The free thread then takes the next codelet from the codelet pool. Once all the threads finish their work and there are no more codelets in the pool, the whole computation completes.

#### Algorithm 2 The pseudo code of the fine-grain 64-point FFT algorithm

```

input: Array D with input data

Array W with pre-computed twiddle factors

output: Array D with final results

Data: Q is a codelet pool that stores all the ready codelets

cnt is a 2-D array that counts the satisfied dependency of each codelet

PSEUDO CODE:

Bit_reversal(D) in parallel;

N \leftarrow D.length;

last\_stage \leftarrow \lceil log_2N/6 \rceil - 1;

for t_{-}id = 0 to N/64 - 1 do

Q \leftarrow Q \cup \{(0, t_{-}id)\};

end for

for each element e in cnt do

e \leftarrow 0;

end for

while Q \neq \emptyset in parallel do

(stage, t_{-}id) \leftarrow Q.pop();

if stage \neq last\_stage then

FFT_64p_kernel(D,W,stage,t_id);

for child = 0 to 63 do

child\_id = \text{Get\_child\_id}(t\_id, child);

cnt[stage + 1, child\_id] + +;

if cnt[stage + 1, child\_id] == 64 then

Q \leftarrow Q \cup (stage + 1, child\_id);

end if

end for

FFT_last_stage_kernel(D,W,stage,t_id);

end if

end while

```

Assume the parent codelet be the *i*th codelet in stage j, and its kth child be the lth codelet in stage j + 1, then

$$l = \lfloor \frac{i}{64^{j+1}} \rfloor \times 64^{j+1} + i \mod 64^{j+1} \mod 64^j + k \times 64^j$$

(3.1)

In this algorithm, every 64 children codelets share the same 64 parent codelets. If codelets  $A0, \ldots, A63$  are the 64 parent codelets of codelet B0, then there will be another 63 codelets  $B1, \ldots, B63$  whose parents are also  $A0, \ldots, A63$ . For example, the 80th codelet in stage 3 is the 0th child of its 64 parent codelets in stage 2, if we apply j = 2, k = 0 and the following i to the above formula. The  $t\_id$  i.e. i in the above

formula of its 64 parents are  $80 + 4096 \times m$  where m = 0, 1, ..., 63. Using the above formula again, we can verify that the 4176th codelet in stage 3 is the next child of the same 64 parent codelets by applying j = 2, k = 1, and l = 4176. Therefore, every 64 codelets share a synchronization counter.

#### Guided Fine-Grain Algorithm

According to the property of the codelet execution model, the fine-grain FFT algorithm is determinate (see Section 2.4). However, the execution order of the codelets is not guaranteed in different runs. Both the initial arrangement of the codelets in the codelet pool and the execution time of the codelets in runtime influence the execution order. A good execution order may achieve more balanced memory accesses to the off-chip memory banks. From the observations, the codelets in the early stage has heavy memory contention on  $bank \ \theta$  and the codelets in the last few stages (especially the last stage) have a balanced workload of memory bandwidth. Therefore, we should break the stage order to make the late-stage codelets executed as early as possible. However, due to the data dependency, children codelets can only be executed after their parent and ancestor codelets complete.

We design a guided fine-grain FFT algorithm to guide the execution order to improve the memory bandwidth usage. Firstly, we divide the stages into two parts. We choose an integer i. Stages 0 to i are called early stages and the rest are called late stages. Then we apply two steps of the fine-grain FFT algorithm. In the first step, the codelets in the early stages are executed. Then a barrier is used to ensure the completion of all codelets in early stages. In the second step, a last-in-first-out (LIFO) codelet pool is used to store the codelets of stage i+1 to arrange a proper order that make the codelets in the last stage satisfy their dependencies as soon as possible. In such a way, the codelets in the last stage are more likely to be executed earlier. As a result, more balanced workload on the 4 DRAM banks are achieved. Algorithm 3 shows our guided fine-grain FFT algorithm using the last two stages as the late stage.

#### 3.1.3 Randomization on DRAM Bank Accesses by Hashing

An alternative solution to balance the memory workload is to randomize the memory addresses of the elements in the twiddle factor array W. Note that the data are always accessed in a balanced pattern on the 4 banks by codelets in each level. The randomization can be achieved by a perfect hash function

$$f: X \to X$$

where  $X = \{0, 1, ..., M - 1\}$  and M is the total number of elements in W. Now the ith element of W will be stored in W[f(i)]. In such a way, the addresses of all the elements in W are randomized. The accesses to them have the balanced workload on the four off-chip memory banks.

In practice, a perfect hash function is too expensive to implement. Instead, we use the bit reversal function BR to replace f. Let  $i = (b_0b_1...b_k)_2$ , then BR is defined as follows:

$$BR(i) = (b_k...b_1b_0)_2$$

Figure 3.3 shows the access rates of the 4 off-chip memory banks by randomizing of the twiddle factor addresses using the bit reversal function. We can see that the memory accesses on the 4 memory banks are balanced. However, because of the overhead of the hash function, the memory address randomization method doesn't always achieve better performance. The detailed experimental results will be shown in Section 3.2.

#### 3.2 Experiment

In this section, we provide and analyze the experimental results of different implementations of FFT algorithm which are described in Section 3.1.

#### 3.2.1 Task Size and Theoretical Peak Performance

In this section, we calculate the theoretical peak performance of the FFT algorithm on the Cyclops-64 node. We assume that the input data size is so large that both

**Figure 3.3:** Access rates of the 4 off-chip memory banks in the fine-grain FFT algorithm with randomized twiddle factor addresses. By using the hash function, all banks are accessed in a uniform manner. The bandwidth resource on each bank can be fully used.

the data array and twiddle factor array are stored in the off-chip memory. The task or codelet size affects the theoretical peak performance because larger size leads to less amount of off-chip memory accesses. We choose the task or codelet size as 64 point butterfly computation, since too much on-chip memory is required and the scratchpad limit is exceeded for larger task or codelet size.

Figure 3.4 shows the best execution time of the fine-grain FFT algorithm using various codelet sizes. As we expected, 64-point FFT outperforms the algorithms with smaller codelet sizes.

The theoretical peak performance can be calculated as follows:

$$peak = \frac{\# of floating point operations}{theoretical exectime}$$

$$= \frac{5 \times N \times log_2 N}{exectime per task \times \# of tasks}$$

(3.2)

# of

$$tasks = \frac{N}{64} \times \lceil \frac{log_2 N}{log_2 64} \rceil$$

(3.3)

**Figure 3.4:** The best execution time of the fine-grain FFT algorithm for 156 threads units running in parallel and a global input data set of  $2^{19}$ . 64-point FFT codelets perform best. The Y axis shows the execution time in cycles. The X axis shows the number of data points given as input to each codelet.

$$exectime\ per\ task = \frac{(64 + 64 + 63) \times 16Bytes}{DRAM\ bandwidth}$$

(3.4)

where N is the data size. To simplify the computation, we remove the ceiling function in Equation 3.3. The removal does not reduce the theoretical peak performance because it will decrease the denominator in Equation 3.2. Equation 3.4 is calculated as follows: Each task needs to load 64 elements from the data array, load 63 elements from the twiddle factor array, and store 64 elements to the data array. Each element takes 16 bytes because it is a double-precision complex number. If the off-chip memory contention does not happen, we get the best execution time of a task as shown in Equation 3.4. The DRAM bandwidth on Cyclops-64 is 16 GB/sec as shown in [37]. So we get the following theoretical peak performance from Equations 3.2, 3.3, and 3.4.

$$peak = \frac{5 \times N \times log_2 N \times 64 \times 6 \times 16G}{N \times log_2 N \times (64 + 64 + 63) \times 16}$$

$$= 10 GFLOPS \tag{3.5}$$

As shown in Equation 3.5, the theoretical peak performance of the FFT algorithm on Cyclops-64 is 10 GFLOPS when the data array and twiddle factor array are stored in the off-chip memory.

#### 3.2.2 Experimental Setup

We implement FFT on the FAST simulator [15] which is a functionally-accurate simulator. It models the memory hierarchy of the Cyclops-64 architecture, including the latencies and bandwidth of each memory segment. The input data are double-precision complex numbers and put into off-chip DRAM. The twiddle factors are precomputed and stored in DRAM as well. We choose 64 as task size and vary input size from  $2^{15}$  to  $2^{22}$  using 156 threads. Besides,  $20, 40, \ldots, 140, 156$  threads are used to run  $2^{19}$  as the input size. We use 156 of the 160 threads because the remaining 4 thread units are reserved for the OS kernel.

In the experiments, we tested 5 versions of the FFT algorithms, and we report their results using 6 types of results. They are described in Table 3.1: coarse, coarse hash, fine (divided between fine worst and fine best), fine hash and

| Name        | Description                              |

|-------------|------------------------------------------|

| coarse      | Coarse-grain synchronization             |

| coarse hash | Coarse-grain synchronization with hashed |

|             | twiddle factor array                     |

| fine worst  | Worst execution time for fine-grain      |

|             | synchronization                          |

| fine best   | Best execution time for fine-grain       |

|             | synchronization                          |

| fine hash   | Fine-grain synchronization with hashed   |

|             | twiddle factor array                     |

| fine guided | Guided fine-grain synchronization        |

**Table 3.1:** Description of the various methods used to perform FFT on Cyclops-64. fine best and fine worst are results reported for the fine algorithm. Other results are named after the algorithm described in the right hand side column.

**Figure 3.5:** The execution time of 5 versions of FFT algorithms on Cyclops-64. The X axis shows the various input sizes of FFT. The Y axis shows the execution time. Lower is better.

fine guided. In the fine-grain algorithm, we found that the initial order of the ready codelets in the concurrent pool may affect the performance a lot. So we show both the worst case and the best case of the fine-grain algorithm in Figure 3.5 and 3.6 as fine worst and fine best, respectively.

## 3.2.3 Major Observations

From our experimental results, the major observations are shown as below:

- 1. The performance of fine best, fine hash, and fine guided are close and outperforms coarse, coarse hash and fine worst which also perform close;

- 2. fine best performs the best and coarse hash performs the worst;

- 3. When the input data size is small, fine hash outperforms fine guided. However, when input data size is large, fine guided outperforms fine hash.

The detailed experimental results and analysis are described in the following sections.

# 3.2.4 Performance of the Various FFT Algorithms

Figure 3.5 shows the performance of the 5 versions when the input data size varies from  $2^{15}$  to  $2^{22}$ . From Figure 3.5, we see that:

- 1. fine guided always performs between fine best and fine worst and close to fine best. The reason is that fine guided takes advantage of a proper codelet execution order that improves the memory access balance.

- 2. fine hash performs better than fine guided when the data input size is small. For example, when the data input size is 2<sup>18</sup>, fine hash is 7% faster than fine guided. However, when the data size increases the fine guided becomes faster (e.g., 1% faster for 2<sup>22</sup> input size) than fine hash. The reason is that the overhead of the bit reversal function increases on larger input sizes due to the work of handling more bits for each element. So our conjecture is that the performance gap between the fine guided and the fine hash will increase as the input data set gets higher. However, we are unable to test larger input sizes due to the time it takes to run our program on the simulator.

- 3. coarse hash always performs the worst, because of the combined overheads of the hash function and of the barrier which lead to unnecessary stalls in the codelet execution.

## 3.2.5 Scalability and Speedup

Figure 3.6 shows the performance of the 5 versions of FFT algorithms on various number of working thread units. We tested from 20 to 156 thread units on the data input size 2<sup>19</sup>. We do not test with fewer than 20 threads units or with larger input sizes due to the limitations of real-life execution time when using the simulator. From the figure we can see that:

- The fine hash and fine guided scale better than the other algorithms. They reach near linear speedup in our tests. fine hash and fine guided perform almost the same, with less than 1% difference. This is because both of the algorithms have more balanced workloads on the off-chip memory banks than the others. In fact, fine hash has an almost perfect balanced workload. However, it does not outperform fine guided due to the overhead of the hash function.

- coarse and coarse hash perform worst. For example, fine guided is about 46% faster than coarse whatever number of thread units we use. The reason are analyzed in Section 3.1. coarse suffers from memory contention on bank 0 in the early stages of the computation. coarse hash, however, suffers from the

**Figure 3.6:** Performance of 5 versions of FFT algorithms on Cyclops-64 for an input size of  $2^{19}$  data elements and 64-point butterfly codelets. The X axis represents the number of thread units used in the computation. The Y axis features the resulting performance (in GFLOPS). Higher is better.

overhead of the hash function computation. Moreover, both algorithms suffer from the overhead of the barriers.

• fine exhibits unstable performance. When we exchange the initial order of the codelets, the performance fluctuates a lot. We found that fine best reaches more or less the same performance as fine hash and fine guided. Moreover, fine worst has more or less the same performance as coarse and coarse hash. This is because the different initial order affects the workload balance of the off-chip memory banks.

## 3.3 Related Work

Sequential and parallel implementations of FFT have been widely studied in the past. FFTW [31, 30, 32] is one of the most famous work on FFT implementation. In FFTW, a planner is used to efficiently divide the whole one- or multi- demensional FFT computation into codelets. Although the name is the same, the concept of the codelet in FFTW is different from that is described in section 2.4. The codelets in FFTW are only some straight-line code that performs a part of the whole FFT computation. However, the codelets in the codelet model is based on dataflow and involve relationship

represented by data dependencies among them to synchronize the execution. Based on FFTW, UHFFT [55, 3], and PFFT [62] are developed to make the FFT computation work efficiently on multi- and many- core systems.