# DEVELOPMENT AND IMPLEMENTATION OF AN FPGA-BASED CONTROL SYSTEM FOR A PASSIVE, DISTRIBUTED APERTURE MILLIMETER-WAVE IMAGING SYSTEM

by

James Lawrence Bonnett

A thesis submitted to the Faculty of the University of Delaware in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Computer Engineering

Spring 2015

© 2015 James Lawrence Bonnett All Rights Reserved ProQuest Number: 1596829

## All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest 1596829

Published by ProQuest LLC (2015). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 - 1346

# DEVELOPMENT AND IMPLEMENTATION OF AN FPGA-BASED CONTROL SYSTEM FOR A PASSIVE, DISTRIBUTED APERTURE MILLIMETER-WAVE IMAGING SYSTEM

by

## James Bonnett

| Approved: |                                                                   |

|-----------|-------------------------------------------------------------------|

| 11        | Dennis Prather, Ph.D.                                             |

|           | Professor in charge of thesis on behalf of the Advisory Committee |

|           |                                                                   |

| Approved: |                                                                   |

| 11        | Kenneth Barner, Ph.D.                                             |

|           | Chair of the Department of Electrical and Computer Engineering    |

|           |                                                                   |

|           |                                                                   |

| A mmoved. |                                                                   |

| Approved: | Babatunde A. Ogunnaike, Ph.D.                                     |

|           | Dean of the College of Engineering                                |

|           | Dean of the conege of Engineering                                 |

|           |                                                                   |

|           |                                                                   |

| Approved: |                                                                   |

|           | James G. Richards, Ph.D.                                          |

|           | Vice Provost for Graduate and Professional Education              |

#### **ACKNOWLEDGMENTS**

I would like to thank my wife, Lindsay Bonnett, my parents, Paul and Wendy Bonnett, and the rest of my family for their constant support and encouragement to push the boundaries of my abilities, as well as the occasional push to help me hold my face to the fire.

I also wish to thank all of my friends and colleagues at the University of Delaware, EM Photonics, and Phase Sensitive Innovations. Special thanks to my adviser, Dennis Prather, and my friend and mentor Petersen Curt, without whose patience and direction this work would not have been possible.

# TABLE OF CONTENTS

| Chap | ter                      |                                  |                               |                        |                                                |          |

|------|--------------------------|----------------------------------|-------------------------------|------------------------|------------------------------------------------|----------|

| 1    | INT                      | RODU                             | CTION                         |                        |                                                | 1        |

|      | 1.1<br>1.2               |                                  |                               |                        |                                                |          |

| 2    | THE                      | E PSI IN                         | MAGING                        | SYSTEM                 |                                                | 4        |

|      | 2.1<br>2.2<br>2.3<br>2.4 | Black<br>Propa                   | body Radgation                | iation                 |                                                | 5        |

| 3    | ELE                      | CTRO                             | NIC PHA                       | SE CONTR               | OL METHODOLOGY                                 | 14       |

| 4    | ITE                      | RATIO                            | NS OF S                       | YSTEM DES              | SIGN                                           | 20       |

|      | 4.1<br>4.2               |                                  |                               |                        |                                                |          |

|      |                          | 4.2.1<br>4.2.2<br>4.2.3<br>4.2.4 | System FMC30                  | Topology               | nd Receiver30_RevB                             | 24<br>25 |

|      |                          |                                  | 4.2.4.1<br>4.2.4.2            |                        | erfaceitioning                                 |          |

|      |                          |                                  |                               | 4.2.4.2.1<br>4.2.4.2.2 | Current Signal Translation Input Amplification | 30       |

|      |                          |                                  | 4.2.4.3<br>4.2.4.4<br>4.2.4.5 | Bus Multip             | perationlexing                                 | 32       |

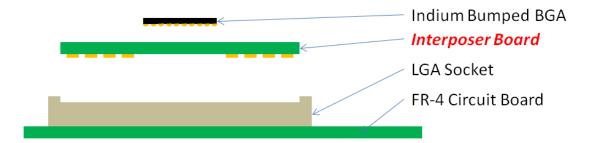

|     | 4.2.5  | Detector  | Interposer                           | . 37 |

|-----|--------|-----------|--------------------------------------|------|

|     |        | 4.2.5.1   | Overview                             |      |

|     |        | 4.2.5.2   | FPA Integration                      | 40   |

|     | 4.2.6  |           | tion30                               |      |

|     | 4.2.7  |           | IEW Interface                        |      |

|     | 4.2.8  | Image A   | cquisition System                    | 45   |

|     | 4.2.9  | Pathfind  | er Integration                       | 46   |

|     |        | 4.2.9.1   | Phase-Feedback Dampening             | 48   |

|     |        | 4.2.9.2   | Flat-Flex Crosstalk Mitigation       | 49   |

|     |        | 4.2.9.3   | SPI Update Level Transition          | .51  |

|     | 4.2.10 | System    | Performance                          | . 52 |

| 4.3 | 30 Cha | annel EC  | Prototype                            | .53  |

|     |        |           | ••                                   |      |

|     | 4.3.1  |           | W                                    |      |

|     | 4.3.2  | Receive   | r30RevC                              | . 55 |

|     |        | 4.3.2.1   | Connector Pinout Modifications       |      |

|     |        | 4.3.2.2   | Comparator Circuit Modifications     | . 58 |

|     |        | 4.3.2.3   | Space-Reduction Measures             | .59  |

|     | 4.3.3  | _         | _RevB                                |      |

|     | 4.3.4  | Distribu  | tion55_RevA and RevB                 | 61   |

|     |        | 4.3.4.1   | Distribution55_RevB Updates          | 63   |

|     |        | 4.3.4.2   | Distribution Board Connector Testing | 64   |

|     | 4.3.5  | Firmwar   | re and Software Improvements         | 65   |

|     |        | 4.3.5.1   | Operational Software Modularization  | 65   |

|     |        | 4.3.5.2   | Camera Capture Improvements          |      |

|     | 4.3.6  | System    | Integration                          | 68   |

|     |        | 4.3.6.1   | Vibration Testing                    | 69   |

|     |        |           | Temperature Testing                  |      |

|     |        | 4.3.6.3   | System Performance                   |      |

| 4.4 | 220-C  | hannel E0 | C Prototype                          | .73  |

|     |        |           |                                      |      |

|     | 4.4.1  | Overvie   | W                                    | 74   |

|      | 4.4.2    | Receiver220_RevA                    | 75 |

|------|----------|-------------------------------------|----|

|      | 4.4.3    | Distribution55_RevC                 | 78 |

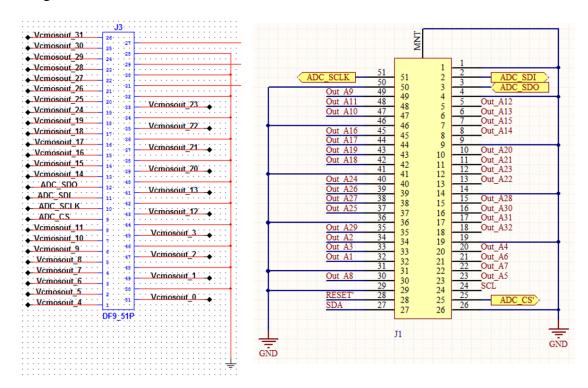

|      | 4.4.4    | Control220 PCB                      | 79 |

|      | 4.4.5    | Embedded Image Acquisition System   | 83 |

|      |          | Power Distribution PCB              |    |

|      | 4.4.7    | Firmware and Software modifications | 85 |

|      | 4.4.8    | System Integration                  | 86 |

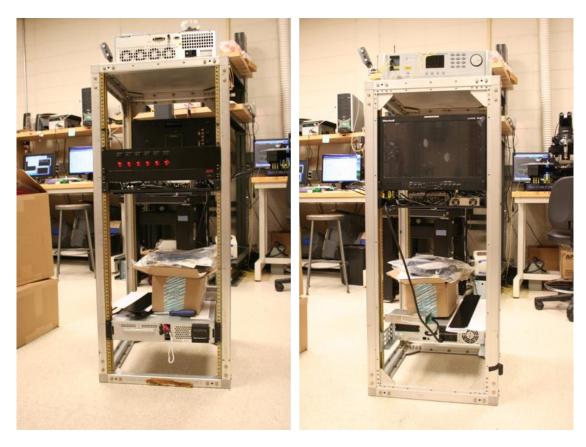

|      | 4.4.9    | Control Rack                        | 88 |

| 5    | EC PROTO | OTYPE FIELD TESTING                 | 90 |

| 6    | CONCLUS  | ION                                 | 95 |

| REFE | ERENCES  |                                     | 96 |

# LIST OF FIGURES

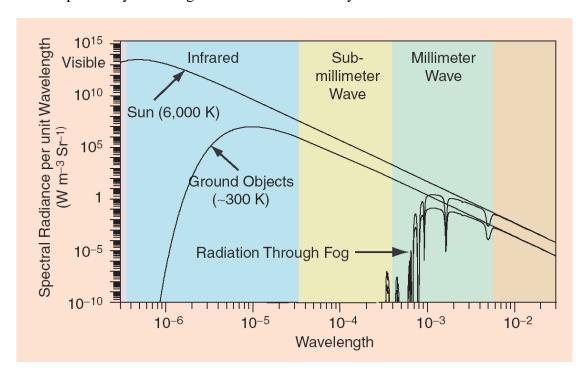

| Figure 2.1 | Passive blackbody radiance through 1km fog                                                                                                                                                                                                                                                          |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

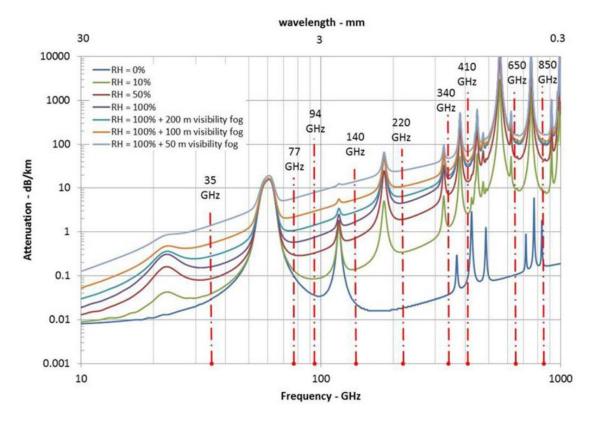

| Figure 2.2 | Graphical representation of atmospheric attenuation of electromagnetic radiation with relation to frequency. Local minima are noted, and of particular interest for imaging modalities. This plot was generated by PSI using atmospheric codes developed for the North Atlantic Treaty Organization |

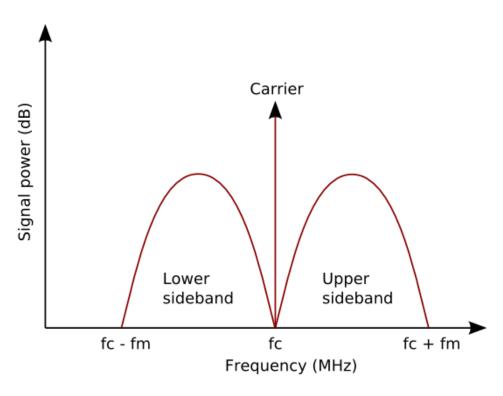

| Figure 2.3 | A graphical illustration of sidebands and how they appear on the electromagnetic spectrum                                                                                                                                                                                                           |

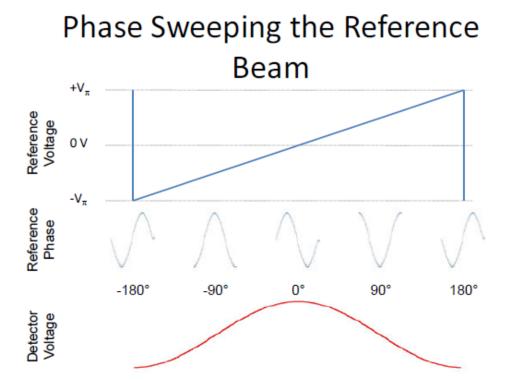

| Figure 3.1 | Sweeping a reference with a DC voltage allows the creation of an interference pattern which varies at a frequency more easily manageable by the control system                                                                                                                                      |

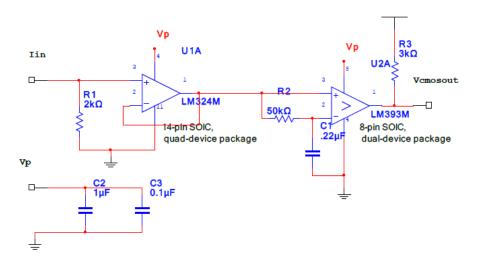

| Figure 3.2 | Schematic of original interference readout circuit for phase detection 17                                                                                                                                                                                                                           |

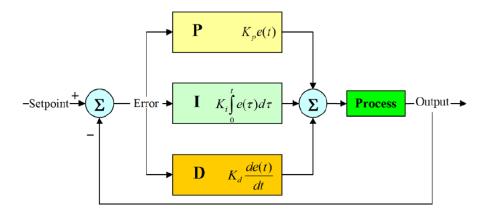

| Figure 3.3 | Phase error computation process, in which three feedback branches are summed to minimize steady-state error, overshoot, and settling time                                                                                                                                                           |

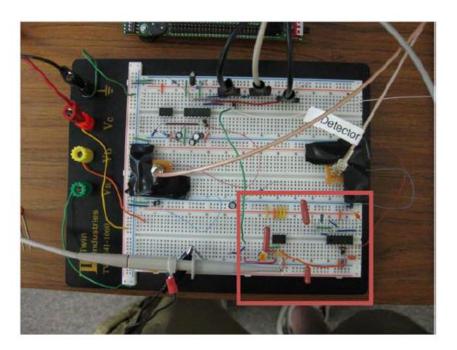

| Figure 4.1 | Original solderless breadboard prototype of the phase detection circuitry, indicated by the red square. The feedback distribution prototype circuitry can also be seen to the upper left of the figure 20                                                                                           |

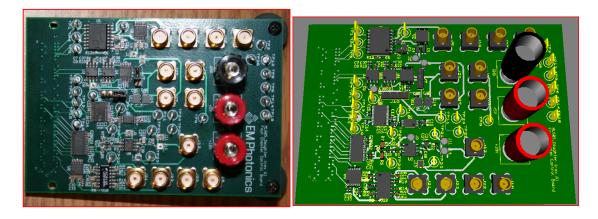

| Figure 4.2 | A picture of the 4-channel prototype PCB together with a software-<br>generated 3D rendering of the same                                                                                                                                                                                            |

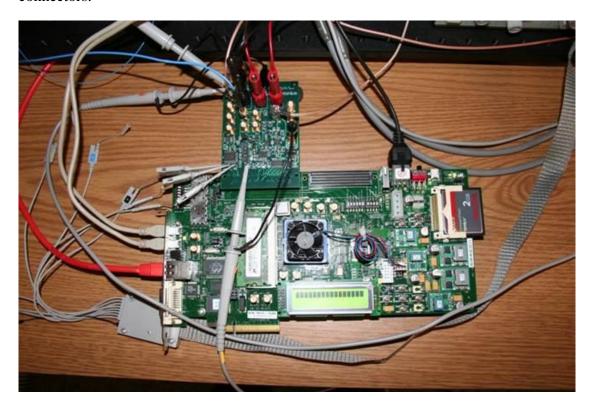

| Figure 4.3 | The 4-Channel Prototype PCB mated to a Xilinx ML-605 Motherboard under test                                                                                                                                                                                                                         |

| Figure 4.4 | Pathfinder Electronics System Diagram                                                                                                                                                                                                                                                               |

| Figure 4.5 | The FMC30 PCB attached to its ML605 carrier                                                                                                                                                                                                                                                         |

| Figure 4.6 | Detector Interposer PCB is shown at right, original PSI receiver layout is shown at left. The addition of the interposer removes the need for 40x optical magnification and occupies significantly less space.                                                                                      |

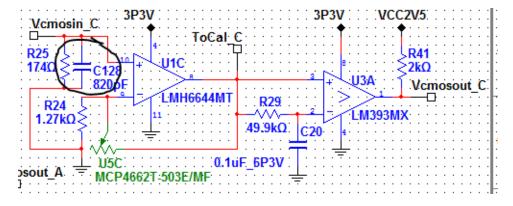

| Figure 4.7  | Receiver 30 Trans-impedance amplifier unit cell, showing input amplification and translation, as well as output digitization                                                                                                                                 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

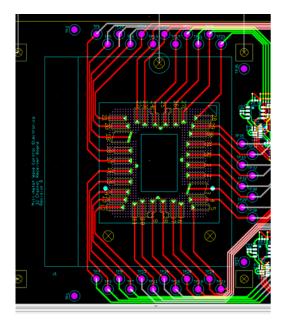

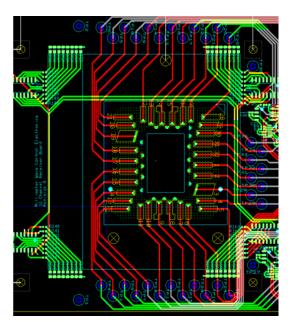

| Figure 4.8  | A comparison of the layouts of the Receiver30_RevA (left) and Receiver30_RevB. The addition of alignment LEDs and the necessary driving circuitry is showing surrounding the Detector Interposer socket. Additional ADC channels are also present            |

| Figure 4.9  | Modifications to the input circuitry of the Receiver board include the addition of a low-pass filter                                                                                                                                                         |

| Figure 4.10 | Conceptual rendering of the Detector Interposer PCB and its interfaces                                                                                                                                                                                       |

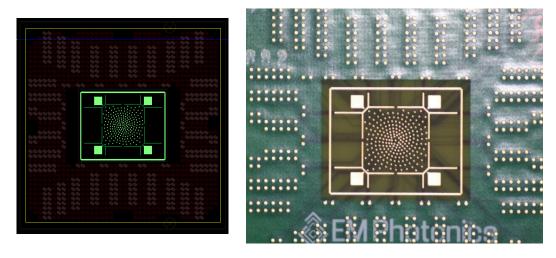

| Figure 4.11 | A design rendering of the Detector Interposer PCB (left) next to a photo of the physical PCB (right). Input channels are routed from the spiral at the center of the PCB to exposed pads on the PCB underside which are also exposed for probing on the top  |

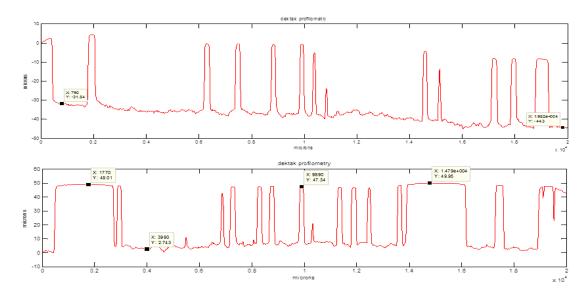

| Figure 4.12 | Sample planarity traces taken of Detector Interposer PCBs. The peaks indicate areas of copper with valleys of FR4 in between. While the top graph shows considerable variance in pad height, the bottom figure is much more planar after polishing           |

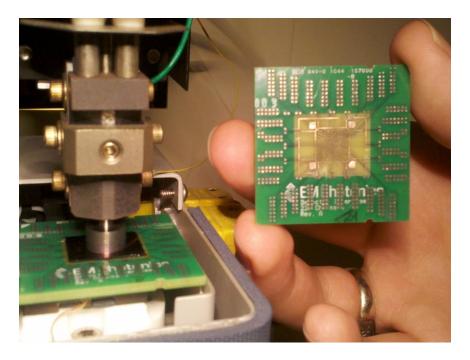

| Figure 4.13 | A bare Detector Interposer PCB is shown next another of the same, which is undergoing the process of having an FPA flip-chip bonded to its upper surface                                                                                                     |

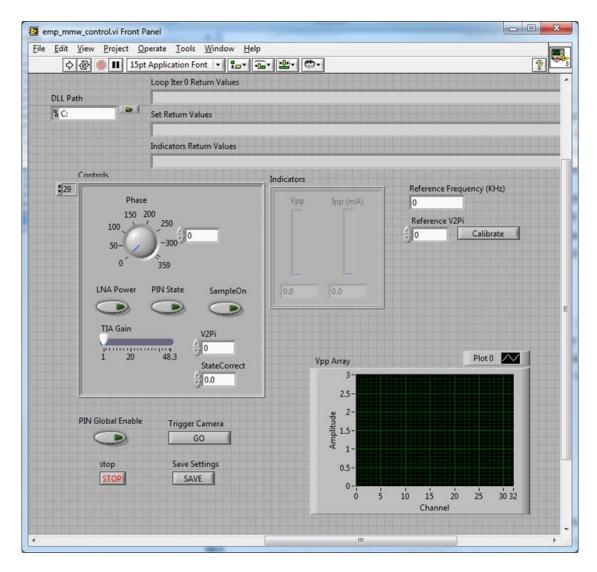

| Figure 4.14 | Front panel of the LabVIEW VI we developed for interfacing with the Pathfinder control system                                                                                                                                                                |

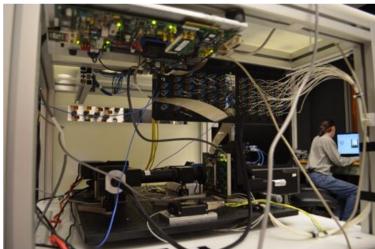

| Figure 4.15 | Pathfinder phase control electronics are shown under test prior to integration. Left to right: Distribution30, Xilinx ML-605 with custom FMC30 PCB, and Receiver30_RevA (sans Detector Interposer - empty socket). Input is provided by the test clips shown |

| Figure 4.16 | Phase control electronics are shown as integrated with the Pathfinder Imaging system. PCBs include the Receiver (left), the Xilinx ML-605 with custom FMC-30 PCB (center), and the Distribution30 (right) 47                                                 |

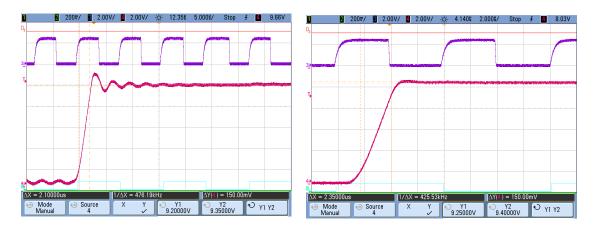

| Figure 4.17 | Underdamped LNA control output is seen to the left. Critically-damped LNA control output is seen to the right                                                                                                                                                |

| Figure 4.18 | Signal errors caused by crosstalk of high-frequency signals are shown, measured from Pathfinder control electronics                                                                                                                                                                                         | 50         |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

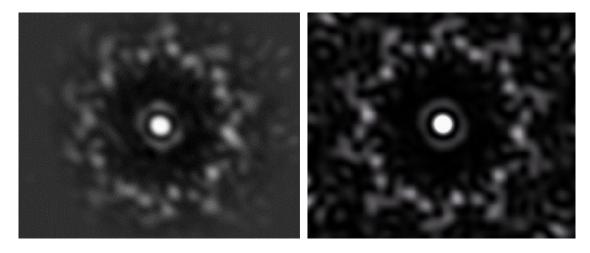

| Figure 4.19 | Pathfinder IIB PSF comparison of measured results (left) to simulated (right)                                                                                                                                                                                                                               | 52         |

| Figure 4.20 | A sample of passive images taken with the Pathfinder IIB                                                                                                                                                                                                                                                    | 53         |

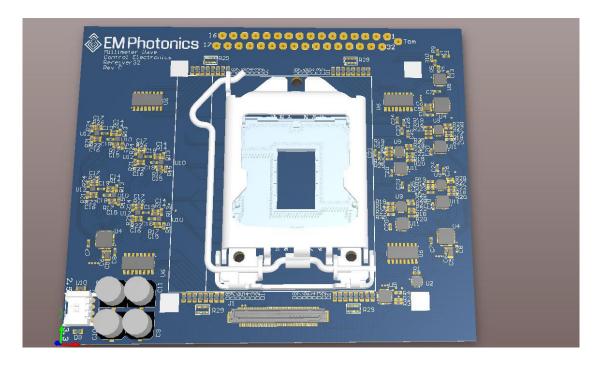

| Figure 4.21 | A computer-generated rendering of the completed Receiver30_RevC PCB                                                                                                                                                                                                                                         | 5 <i>5</i> |

| Figure 4.22 | A comparison of connector pinouts from the Receiver30_RevB (left) and the Receiver30_RevC (right). The rearrangement of the signals appears subtle, but had a marked effect on our crosstalk issues                                                                                                         | 57         |

| Figure 4.23 | A computer-generated rendering of the FMC_30_RevB                                                                                                                                                                                                                                                           | 50         |

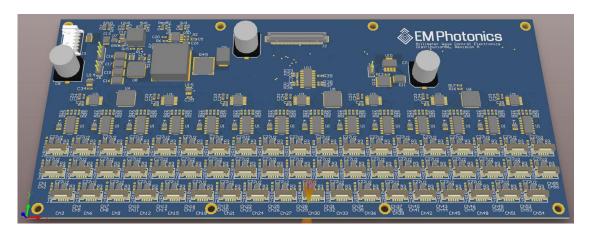

| Figure 4.24 | A computer-generated rendering of the Distribution55_RevA PCB                                                                                                                                                                                                                                               | 51         |

| Figure 4.25 | Our flat-flex ZIF connector evaluation setup, comprised by a custom test PCB affixed to a vibration piston. Connection integrity is monitored by the oscilloscope, with any events recorded by a LabVIEW VI running on the control PC                                                                       | 65         |

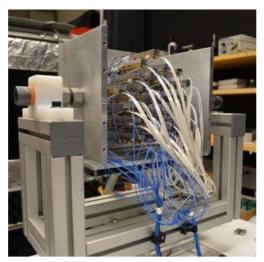

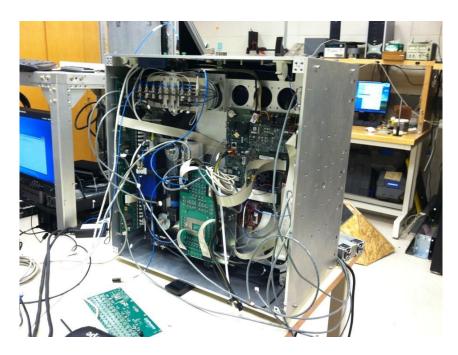

| Figure 4.26 | Pictures showing our phase control electronics integrated with the 30-Channel EC Prototype imaging system                                                                                                                                                                                                   | 68         |

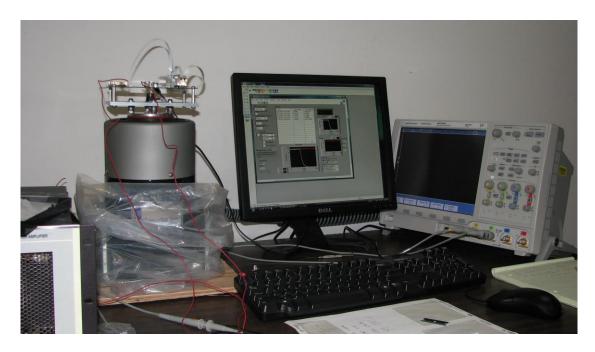

| Figure 4.27 | Vibration test setup. Instrumentation shown includes FPGA control electronics PCB, Distribution electronics PCB, phase control electronics power supply, vibration solenoid, vibration solenoid power amplifier, PC for vibration control, PC for phase control and data capture, and digital oscilloscope. | <b>7</b> 0 |

| Figure 4.28 | Table showing comparison of the EC Prototype phase control electronics performance with and without vibration to that of the original 4-Channel prototype hardware                                                                                                                                          | 71         |

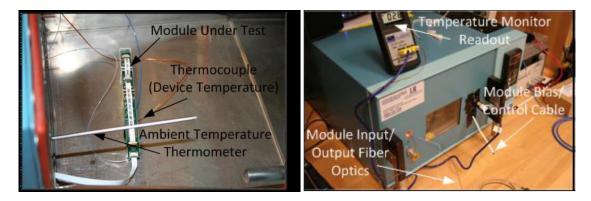

| Figure 4.29 | (left) PSI Upconversion Module undergoing temperature testing inside our temperature-control chamber. (right) The temperature control chamber is shown with some relevant test equipment.                                                                                                                   | 72         |

| Figure 4.30 | PSI Upconversion Module performance is shown to be reasonably steady under high-temperature conditions                                                                                                                                                                                                      | 72         |

| Figure 4.31 | A comparison between the phase-locked point spread functions of the 77GHz 30-Channel EC Prototype (left) and the 35GHz Pathfinder IIB (right)                                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

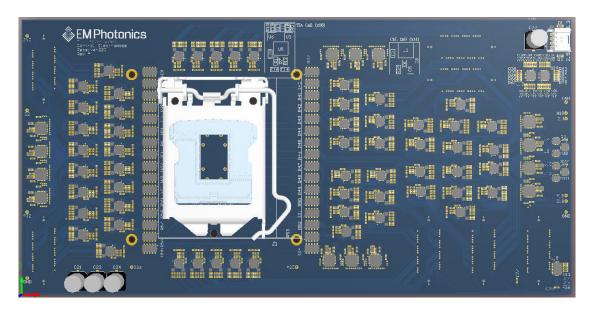

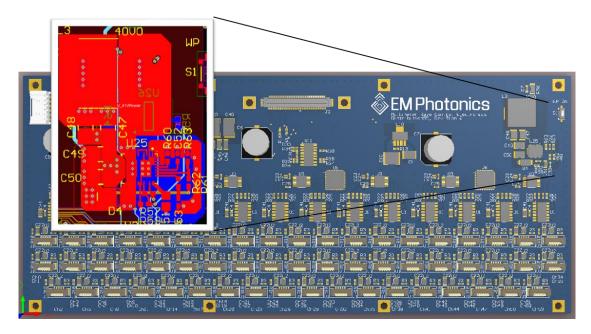

| Figure 4.32 | Computer-generated 3D rendering of the front face of the Receiver220_RevA PCB                                                                                                                                                                             |

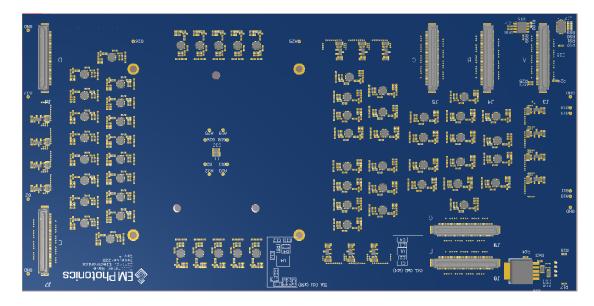

| Figure 4.33 | Computer-generated 3D rendering of the back face of the Receiver220_RevA PCB                                                                                                                                                                              |

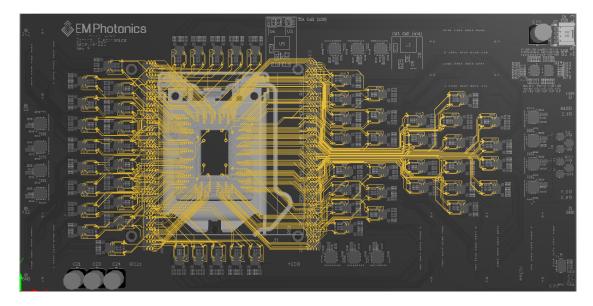

| Figure 4.34 | Composite image of multiple signal layers showing routing of input signals from the Interposer socket to their respective phase-detection unit cells                                                                                                      |

| Figure 4.35 | Computer-generated 3D rendering of the Distribution55_RevC PCB, detailing the addition of the 41V boost circuitry79                                                                                                                                       |

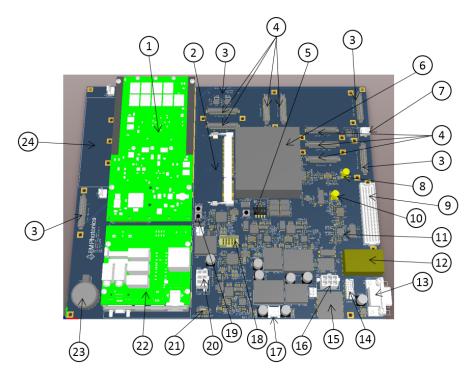

| Figure 4.36 | Computer-Generated 3D rendering the of the Control220 PCB design with annotations and part labels                                                                                                                                                         |

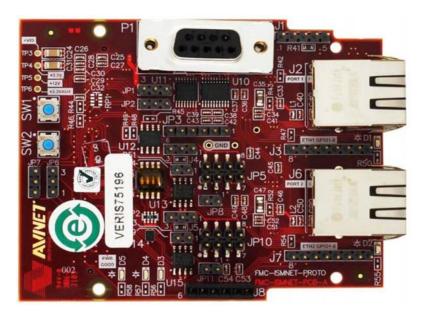

| Figure 4.37 | COTS Ethernet expansion card which was used as a workaround to our problematic Ethernet interface                                                                                                                                                         |

| Figure 4.38 | The COTS SBC utilized in our system to interface with the camera and collect frames                                                                                                                                                                       |

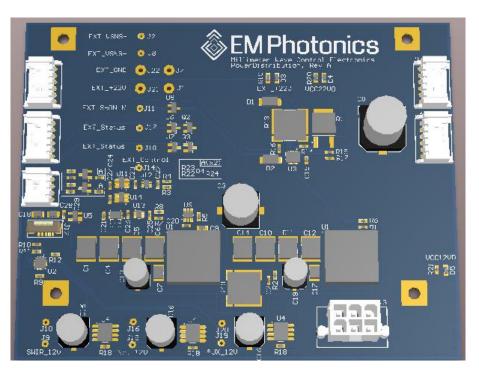

| Figure 4.39 | Computer-generated 3D rendering of the Power Distribution PCB 84                                                                                                                                                                                          |

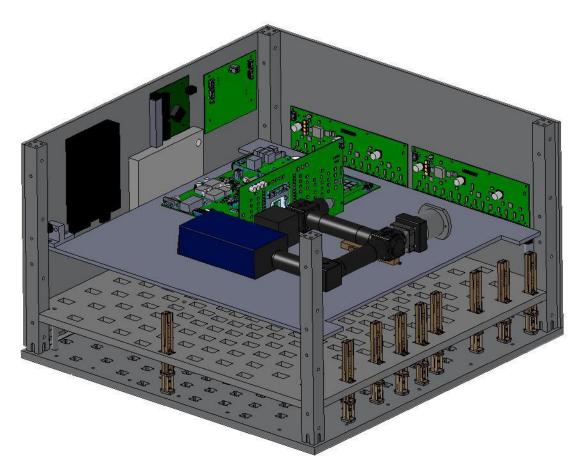

| Figure 4.40 | Computer-generated 3D rendering of the inside of the EC Prototype enclosure, showing the orientation of the RF modules, the Optical Processor, and the Control Electronics. Generated by PSI                                                              |

| Figure 4.41 | The partially-assembled EC Prototype. At this stage, all the electrical components of the system are connected, though not fully installed. This level of integration was the first to allow operational testing of the EC Prototype as a unified system. |

| Figure 4.42 | The EC Prototype, now with the major operational components of the system fully integrated                                                                                                                                                                |

| Figure 4.43 | Front and back view of our custom electronics control test rack89                                                                                                                                                                                         |

| Figure 5.1  | An H-53 flyover pass during field testing in Yuma, AZ90                                                                                                                                                                                                   |

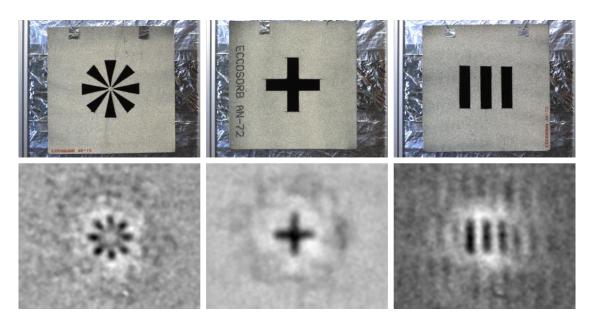

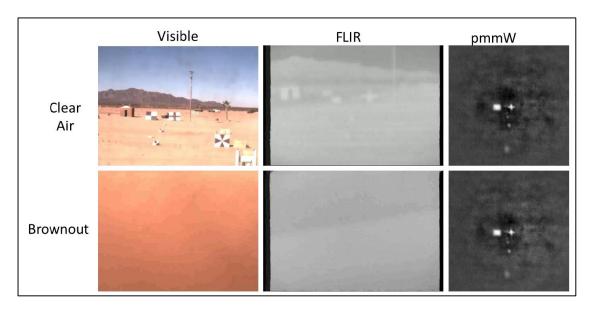

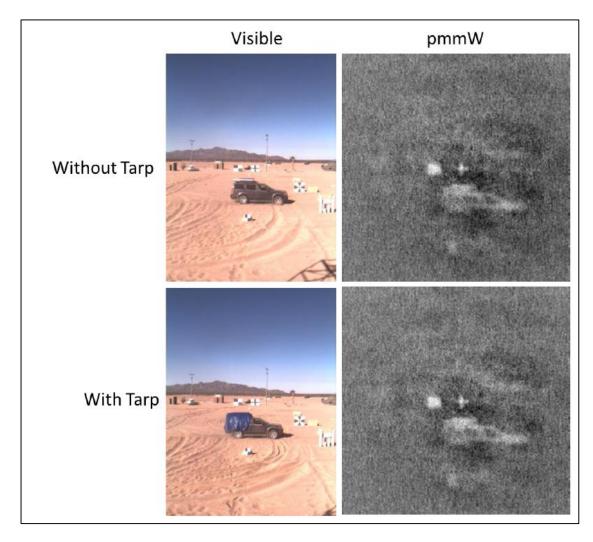

| Figure 5.2 | A comparison of imaging modalities used in field testing, in the presence of both clear air and brownout conditions                                                                                                                                 | . 91 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 5.3 | Imagery taken during field testing of an automobile with a metal tube affixed to its roof, simulating an IRAM (Improvised Rocket Assisted Mortar). The simulated IRAM is still visible in the passive MMW imagery when hidden from sight by a tarp. | . 92 |

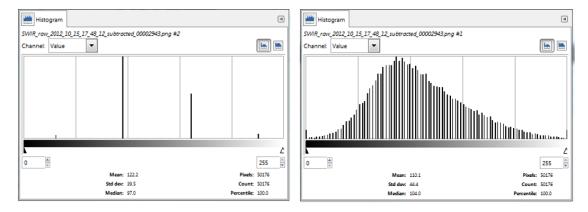

| Figure 5.4 | Histograms of processed images in LabVIEW, before and after field modifications to the processing pipeline. The histogram on the left is a particularly bad example, showing only 4 pixel values, but this was not typical of normal operation      |      |

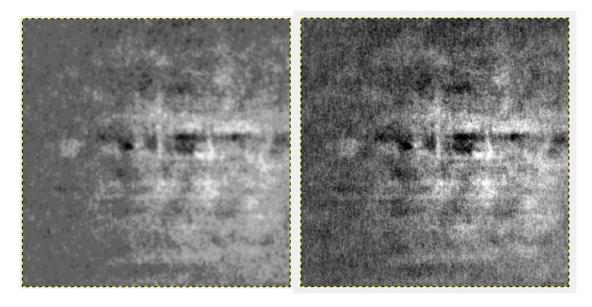

| Figure 5.5 | Images corresponding the histograms shown above. The figure on the left suffers a severe loss of contrast.                                                                                                                                          | . 94 |

#### **ABSTRACT**

Degraded visual environments, particularly those caused by brownout or whiteout, pose one of the most prominent threats to rotary-wing aircraft operating in areas with unimproved landing zones, accounting for nearly half of the losses of rotary-wing aircraft experienced by the Air Force, and providing the leading cause of those suffered by the Army. In an effort to mitigate this threat, Phase Sensitive Innovations has been developing a passive millimeter-wave sensor with the ability to image through the obscurant clouds causing the degraded visual environment. Novel imaging systems such as these likewise require novel control methodologies. In conjunction with PSI, EM Photonics, and the University of Delaware, my research has been focused on developing and implementing such a system.

#### Chapter 1

#### **INTRODUCTION**

#### 1.1 Motivation

Much attention has been focused in recent years on the issue of degraded visual environments (DVE) and safe navigation thereof. Of particular interest is the issue of brownout, or of DVE experienced by aircraft which is caused by clouds of sand, dust, or similar particulates. This is a common obstacle encountered by rotarywing aircraft when landing in unimproved areas, especially in sandy areas such as the desert. One can easily imagine the challenges such an environment would pose as the downwash of an approaching helicopter transforms a sandy landing zone into a sandstorm; all visual reference quickly disappears, leaving the pilot to fly blind. The problem compounds if we consider that this aircraft may be only the first of a convoy, leaving those that follow without a visual reference not only to the ground but also to any aircraft which have already landed. With this situation in mind, it is not difficult to understand why degraded visual environments, particularly brownout, are currently the single largest contributor to military rotary-wing losses<sup>1</sup>. In addition, the impact of missions that must be canceled due to poor visibility cannot be quantified. Brownout effects operational scenarios and endangers helicopter crews, as well as those who depend on their support.

Current sensor suites employed by the military on these airframes that allow pilots to see in the dark or through fog are unable to compensate for these environments. As such, new imaging techniques and modalities are being investigated

Innovations, Inc (PSI) in conjunction with the University of Delaware and under contract with the Navy. This system is of novel design and operates by means of passive detection of millimeter waves (high-frequency RF waves in the range of 10's to 100's of GHz). This program has resulted in several proof-of-concept systems, as well as a fieldable prototype which has now undergone both ground and flight testing. As will be discussed in greater detail later, such a system is inherently sensitive to phase variations induced by vibration, making operation in a harsh environment or onboard an aerial platform unfeasible without the ability to mitigate these variations, necessitating a sophisticated control system. This thesis presents the development of the electronic control systems developed in conjunction with the imaging systems which provide the necessary control functionality that enables the use and deployment of this technology.

#### 1.2 Contribution

During the course of this project, I operated as the second of a two-man electronics development team. The other engineer on this team was Petersen Curt, Senior Engineer at EM Photonics, who was the lead engineer on this project. The design methodology was developed by EM Photonics and has been patented under publication number US 8897656 B2<sup>2</sup>. Our team designed, implemented, and integrated several revisions of the control system based on this design pertaining to developmental prototypes built by PSI. The effort required involved a wide range of disciplines, including analog circuit design, PCB layout, firmware and software generation, and no small amount of troubleshooting.

My contributions have been further detailed in the following publications:

- Thomas E. Dillon; Christopher A. Schuetz; Richard D. Martin;

Daniel G. Mackrides; Petersen F. Curt; James Bonnett; Dennis

Prather "Nonmechanical beam steering using optical phased arrays ",

Proc. SPIE 8184, Unmanned/Unattended Sensors and Sensor Networks

VIII, 81840F (October 04, 2011); doi:10.1117/12.898356;

http://dx.doi.org/10.1117/12.898356

- Martin, Richard, Christopher Schuetz, Thomas Dillon, Daniel

Mackrides, Peng Yao, Kevin Shreve, Charles Harrity, Alicia Zablocki,

Brock Overmiller, Petersen Curt, James Bonnett, Andrew Wright,

John Wilson, Shouyaun Shi, and Dennis Prather "Optical Upconversion Enables Capture of Millimeter-wave Video with an IR

Camera." SPIE Newsroom. 13 Aug. 2012. Web.

<a href="http://spie.org/x89063.xml">http://spie.org/x89063.xml</a>>.

- 3. Petersen F. Curt; **James Bonnett**; Christopher A. Schuetz and Richard D. Martin "Embedded electronics for a video-rate distributed aperture passive millimeter-wave imager ", Proc. SPIE 8715, Passive and Active Millimeter-Wave Imaging XVI, 871508 (May 31, 2013); doi:10.1117/12.2018519; http://dx.doi.org/10.1117/12.2018519

- 4. Christopher Schuetz; Richard Martin; Thomas Dillon; Peng Yao; Daniel Mackrides; Charles Harrity; Alicia Zablocki; Kevin Shreve; James Bonnett; Petersen Curt; Dennis Prather "Realization of a video-rate distributed aperture millimeter-wave imaging system using optical upconversion", Proc. SPIE 8715, Passive and Active Millimeter-Wave Imaging XVI, 87150I (May 31, 2013); doi:10.1117/12.2016138; http://dx.doi.org/10.1117/12.2016138

#### Chapter 2

#### THE PSI IMAGING SYSTEM

To understand the requirements of the electronic control system developed in this project, it is necessary to understand the purpose for which it was designed and likewise to understand the basic concepts behind the imaging system developed by Phase Sensitive Innovations (PSI). PSI's imager operates in the millimeter-wave region of the electromagnetic spectrum, so denoted because the physical wavelength of radiation in this area of the spectrum exists on a range of about 1mm to 1cm. By contrast, other common sources of electromagnetic radiation encountered in the course of daily life range from FM radio waves, as long as 3 or 4 meters, to the so-called 'optical' wavelengths that our eyes are sensitive to, measuring mere hundreds of nanometers, a billion times smaller; between these two common examples sits a wide range of other frequency regimes, each suited to different applications. Millimeter waves in particular are of special interest for a variety of reasons, primarily in relation to their properties regarding three particular physical phenomena, namely scattering, blackbody radiation, propagation, and diffraction, each of which will be addressed in limited detail in the following few paragraphs.

#### 2.1 Scattering

In effect, scattering is at the heart of the brownout issue, and thus I address it first. When an electromagnetic wave, or rather a wave of any type, comes into contact with an object, its reaction with that object depends quite strongly on the ratio of the wavelength of the light to the size of the particle. A very long wave that is incident on

a very small particle will hardly scatter at all (e.g. a typical RADAR signal would hardly be affected by a small object like a baseball), while a much shorter wave would scatter strongly (e.g. optical wavelengths scatter specularly off of a baseball, which is what allows us to see it). Here, then, we can see the inherent physical issue taking place during brownout in that the optical wavelengths with which we see are quite short in relation to the size of the sand and dust particles of the obscurant cloud, and are thus scattered entirely. While visible light ranges from approximately 400 to 700 nanometers, the smallest dust and sand particles are merely a few microns in size, and some are even larger. Even the FLIR (forward-looking-infrared) optics already employed aboard the airframes in question are unable to penetrate the dust cloud, despite a slightly longer wavelength. Attempts have been made to apply computational techniques to imagers operating in the visible and infrared regimes with varying amounts of success, but as of yet these wavelengths cannot yield a solution which can see through the dust cloud. Here we encounter the first advantage of millimeter-waves as they are long enough to pass through the obscurant cloud with little scattering, and thus minimal attenuation. Why stop here, then? If longer wavelengths bring better penetration performance, why not utilize even longer wavelengths? The answer to this basic question lies within the issue of diffraction, which will be addressed in a moment. First we must consider the implications of blackbody radiation.

#### 2.2 Blackbody Radiation

Active imagers must first illuminate their object before imaging it, like a RADAR system, whereas a passive imager operates using the ambient illumination already present in the scene. In the context of the PSI imager, this illumination is

created by blackbody radiation. Blackbody radiation is the emission of electromagnetic radiation as a function of heat. This is commonly seen in daily practice as a hot stove will often glow red when it becomes very hot. Cooler objects also emit blackbody radiation, though we may not be able to see it with the naked eye. As the heat of an object increases, so does the energy, and consequently the frequency, of the emitted radiation. Very hot objects, like a hot stove, can emit at visible frequencies, while people, with a typical core temperature of 98.6 degrees Fahrenheit, radiate in the infrared regime. As we consider cooler and cooler objects we encounter the comparatively cool range of terrestrial blackbody radiation.

Figure 2.1 Passive blackbody radiance through 1km fog<sup>3</sup>

Now we must consider the combination of blackbody radiation with the discussion of scattering above. As shown in Figure 2.1 above, the radiation spectrum

of ground objects follows that of the sun fairly closely up to the infrared range, reaching a peak. Because of this, a passive imaging system operating around this peak would exhibit better performance, but we can also see that radiation through fog drops off dramatically in the lower millimeter-wave regime, making the infrared portion of the chart useless in the context of degraded visual environments. Here we can see quantitatively why existing imaging modalities that make use of this portion of the spectrum fall short in these situations. Given the combination of these factors, millimeter-waves present an attractive solution in terms of both scattering and blackbody radiation.

#### 2.3 Propagation

In addition to the previously mentioned properties regarding scattering and blackbody radiation, millimeter waves have a significant ability to penetrate the atmosphere. As can be surmised, such a quality is absolutely essential in the development of imaging modalities expected to operate at any appreciable range. Loss in propagation through the atmosphere is highly dependent on frequency. Much as radiation from a variety of frequencies may be scattered by obscurants in the air, attenuation of electromagnetic radiation is highly frequency dependent, as shown in figure 2.2 below. Of particular interest are the local minima shown, which correspond to frequencies which are not attenuated to the extent that others are. As can be seen, several frequencies of interest can be found in both the Q-band (33-50GHz) and W-band (75-110GHz). As such, these are the operation frequencies of the various iterations of the PSI imager.

Figure 2.2 Graphical representation of atmospheric attenuation of electromagnetic radiation with relation to frequency. Local minima are noted, and of particular interest for imaging modalities. This plot was generated by PSI using atmospheric codes developed for the North Atlantic Treaty Organization.<sup>4</sup>

#### 2.4 Diffraction

The resolution of any imaging system is limited by diffraction. Even a 'perfect' lens cannot achieve infinite resolution unless it is infinite in extent due to the fundamental physical nature of light. As such, the resolution of an imaging system is typically described by the minimum angle discernable between the focal point of the lens and resolvable points in the image. In the common case of a focal-plane array with a circular lens, this minimum angular resolution is effectively estimated by the Rayleigh Criterion, which defines it as being directly proportional to the wavelength in

question and inversely proportional to the aperture diameter as shown by the following equation:

$$\alpha \approx 1.22 \frac{\lambda}{D}$$

It follows, then, that an imaging system utilizing long wavelengths is at an immediate disadvantage when it comes to resolution, as the aperture must grow in direct proportion to the wavelength to achieve the same level of resolution. This sounds straightforward enough, but only until we consider the sheer extent of the electromagnetic spectrum. Visible light ranging from 400-700nm can be used to capture high-definition imagery with devices small enough to fit inside a cell phone, but a similar device utilizing millimeter-waves would have to be over a thousand times larger to compensate for the difference in wavelength. Such a system would no doubt prove useful for some applications, but would be inappropriate for our purposes of brownout mitigation aboard rotary-wing aircraft.

Much of the diffraction limitation we see here is imposed by the system topology. As mentioned above, most cameras and imaging systems of similar modalities make use of a combination of optical lenses and a focal plane array, but implications of the diffraction limit inherent to such a system topology make it prohibitive to use to image millimeter-waves with an appreciable level of resolution. Systems of this type do indeed exist, but their size and weight make them ill-suited for use on a weight-sensitive aerial platform, particularly rotary-wing aircraft, and as such they are relegated to use on ground platforms or on very large aerial platforms.

In light of this, PSI eschewed the conventional configuration, opting to design their imaging system around a distributed aperture. Where a conventional aperture

would be defined by a single focal-plane array and any relevant lenses, a distributed aperture is comprised by many discrete antennae which are spatially dispersed. A high-profile example of such a system can be seen in use on-board the Lockheed Martin F-35 Lightning II, or Joint Strike Fighter. This system, the Northrop Grumman AN/AAQ-37 DAS (Distributed Aperture System)<sup>5</sup>, consists of an array of high-resolution electro-optical infrared sensors, the combined imagery of which affords the pilot an unobstructed  $4\pi$  steradian view of his surroundings, effectively allowing him to see through the hull of the aircraft.

In the case of the PSI Distributed Aperture Imager (DAI), the aperture is defined by multiple discrete antennae distributed over the front surface of the imager. Each of these distributed channels consists of a horn antenna, a chain of low-noise amplifiers, and a phase modulator. These channels would appear to be analogous to the pixels of a conventional focal-place array, but this is not the case. Rather, they would be better described as components of a wavefront sensor, collecting information relating to the spatial frequencies of incident millimeter waves from which an image can be reconstructed using interferometric imaging techniques. The employment of this approach allows the DAI to achieve the performance of a much larger imaging system without the additional size and weight.

Crucial to the operation of the PSI DAI is the upconversion modulator, which operates by means of frequency modulation in similar fashion to a heterodyne mixer. In typical applications of frequency modulation, ie an FM radio, audio signals (ranging from 10Hz to 14kHz) are modulated onto a carrier of much higher frequency (88 to 107MHz) by varying the instantaneous frequency of the carrier wave. This familiar process is governed by the equation:

$$\cos(a) * \cos(b) = \cos(a+b) + \cos(a-b)$$

If 'a' is taken to be the carrier frequency and 'b' is taken to be the frequency of the encoded data, we can see that two signals are generated at frequencies of a+b and a-b; these are known as sidebands.

Figure 2.3 A graphical illustration of sidebands and how they appear on the electromagnetic spectrum

In similar fashion, information captured from the millimeter-wave regime, in this case ranging from 35 GHz to 77 GHz, can likewise be encoded on higher-frequency carriers such as short-wave infrared light. The implications of this are numerous, but the primary benefit is that information gathered from millimeter waves can be encoded on infrared light, which can easily be imaged without the debilitating effects of

diffraction seen when attempting to image millimeter waves. This carrier is generated by a ~1550nm laser, a wavelength that is very common in the telecommunication industry, and for which sensor arrays can be easily acquired. Imaging with a distributed aperture requires that magnitude and phase information be saved from each detector in the distributed array. Typically this requires the use of distributed Local Oscillators and mixers to down-convert the relevant data for digital storage, requiring fairly intense computational methods (which themselves call for fairly large and heavy computational equipment) for image reconstruction. This complication is mitigated in PSI's system by the use of the aforementioned optical upconversion and interferometric imaging techniques. A faithful reproduction of the wavefront is created in the infrared regime by coherently recombining the sidebands of the infrared carrier on each channel in free space, allowing the realization of an image by measuring the far field of the wavefront with an IR camera, effectively performing a Fourier Transform. This technique allows the back-end of the system to operate as a common infrared camera, which is an easily-accessible and mature technology, and results in higher resolution than would otherwise be possible with a conventional imaging system with the same name number of sensors. To faithfully reproduce the incident wavefront in the infrared regime, the physical layout of the distributed aperture is mimicked by the output fiber-optics of each respective channel by mounting them in a very small silicon array which was itself developed with a special etching process by PSI. This array is sized so as to be proportional to the distributed aperture, but scaled by wavelength, and so great care must be given to the placement of the fibers and the respective optical path-length (OPL) of each channel. These fibers are then allowed to emit to free space, where the carrier frequency and one of the two sidebands are

eliminated by a narrow-bandwidth optical filter, leaving only the modulated image data. This data can then be recorded by placing a SWIR (Short-Wave IR) camera at the focal plane of the optical system.

The unique combination of a distributed aperture with optical upconversion enables unprecedented millimeter wave imaging performance, but also introduces complication in that each channel must be controlled individually. An added complication of a distributed aperture imager is a phenomenon known as 'fringe washing'. The formation of an image requires both coherence and phase calibration, which becomes increasingly difficult to maintain as the number of individual channels in the aperture increases. Differences in the path length of each channel correspond directly to differences in phase between these channels, which must be constrained within the associated coherence length relating to the bandwidth of the system in order for an image to be generated. As such, instabilities in these relative phases caused by effects such as vibration pose a considerable threat to system operation when left unchecked. In the context of millimeter waves, coherence is fairly easy to maintain, as the signals are sensitive to perturbations on the order of their wavelengths, which are uncommon. After upconversion, however, the signals are now sensitive to perturbations on the order of their new wavelengths, which are much smaller and thus the threshold for degradation is much lower. As such, very sensitive phase stabilization is required to maintain the fidelity of the infrared signals.

The unique architecture of the imager developed by PSI presents a collection of unique challenges for a prospective control system. Given that such an imaging system is very novel, it follows that a novel control system must be developed for it so that it may be tailored to its needs.

#### Chapter 3

#### ELECTRONIC PHASE CONTROL METHODOLOGY

In order to normalize the fluctuations in phase produced by each channel, a control methodology had to be developed which was capable of detecting, calculating, and compensating for the perturbations on any given channel in an appreciable amount of time to allow real-time video display without aberration. This methodology was pioneered at EM Photonics and has been published in a patent held by EM Photonics, Inc. Work completed by EM Photonics on this project was likewise performed under contract with the Navy, who funded its development.

The primary function of the electronic control system is to stabilize the phase of each individual channel so as to enable coherent imaging. All modulators in the system are fed by the same laser, causing them to modulate coherently, at least in theory. Also important to the generation of an image is the relative phase of each channel. We know that a phase shift in the frequency domain corresponds to a shift in the time domain, and so variations of relative phase between sensor channels can have a variety of effects on the final image, from shifting focal distance to completely scrambling the image. In practice, however, this phase relation between channels is frequently disturbed by vibration and movement of the system. While the front end of the system operates in the millimeter-wave regime, and is thus sensitive to vibrations proportional to long wavelengths (a few millimeters), the upconverted signals that can be found in the optical processor are sensitive to perturbations on the order of their own wavelengths, about 1550nm (a common telecommunication wavelength in the

infrared (IR) regime). In this context, and fluctuation in the path of the optical fiber on the order of a micron can cause phase fluctuations on the image contribution of that particular channel, and the phase-coherence is broken.

Since all of the modules are intended to be coherent by virtue of being fed by a single laser source, that being coherent by definition, these perturbations can be detected and measured by comparing a given channel with a reference. As such, an additional reference module is added to the system which receives no RF input. The output of this modulator is then interfered optically with those of the signal carrying modulators, creating an interference pattern from which the phase aberrations on the input channel can be inferred. The mechanism of a phase modulator is to convert an input voltage signal into a variation in phase on a given carrier signal. As more voltage is applied, the variation in phase on the carrier signal becomes more pronounced, until it eventually reaches the  $2\pi$  radians (360°) point where it wraps back to its original state. Given this repetitive nature of phase, the range of voltages needed to produce a phase shift from 0-2 $\pi$  (generally referred to as  $V_{2\pi}$ ) can accomplish any adjustment required. Thus, assuming a linear modulator, a signal of increasing linear amplitude would produce the same results as a signal which increases to  $V_{2\pi}$ , returns immediately to 0, and repeats – effectively forming a sawtooth with inflection points at every multiple of  $V_{2\pi}$ . When such a signal is applied to a phase modulator, the output of which is then interfered with another coherent modulator with what should be a constant phase input, the output interference pattern will present as a classic sine wave. Since the phase inputs on the signal modulators are ostensibly constant, varying only by the phase aberrations inflicted on them by vibration or discrepancies in path length, each individual interference pattern will bear the shape of a shifted sine wave.

This shift is then directly proportional to the phase error present on that particular channel, allowing it to be calculated. This relation is shown in Figure 3.1 below.

Figure 3.1 Sweeping a reference with a DC voltage allows the creation of an interference pattern which varies at a frequency more easily manageable by the control system

The next challenge is to devise a way in which this phase error can be automatically detected by a digital system. These signals are easily captured due to the abundance of photodetectors developed to function in this particular wavelength range (~1550nm). However, these signals are analog by nature and cannot be understood or acted upon appreciably by a digital system. The classical solution would be to add an

analog-to-digital converter circuit to the input of each channel, but this design is not always feasible or optimal. Analog-to-digital converters are expensive and would in this case add quite a bit of unnecessary complication to system operation. As discussed earlier, channel signals present in the form of shifted sinusoids. In the context of a system input then, a digital representation of the complete signal would be superfluous information, as only the relative phase offset of the given signal with respect to the system reference is of consequence. As such, the methodology developed consists of analog circuitry which comprises what is essentially an edge detector or 1-bit analog-to-digital converter in practice. The original concept of this circuit is shown below.

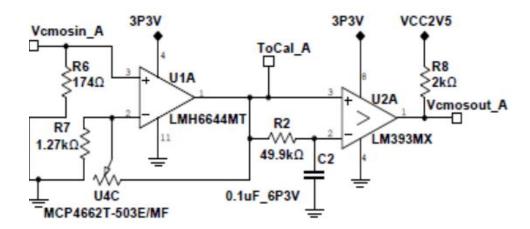

Figure 3.2 Schematic of original interference readout circuit for phase detection

The particulars regarding the operation of the various parts of this circuit will be discussed in more detail in the following sections, but in general the left side of the circuit comprises a trans-impedance amplifier, converting the input current signal from a photodiode to a voltage signal and amplifying it, and the right side of the circuit comprises the comparator circuit. As can be seen, the output of the trans-impedance amplifier is split and one leg is subjected to a low-pass filter, the cutoff frequency of which is tuned to be lower than the expected frequency of the sinusoidal signal. As such, this leg effectively represents a DC average of the original signal, and is connected to the negative terminal of the comparator. The unfiltered signal is then passed without alteration to the positive terminal of the comparator. When the signal value is less than its average, the output is driven low. When the signal is greater than its average, the output is allowed to float high due to the pull-up resistor attached to the output. In this way, the incident sinusoidal waveform is effectively transformed into a square wave, which can more easily be understood by the FPGA control system. Also, the inflection points of the incident signal are preserved in the generated waveform, allowing for calculation of relative phase offset via measurement of temporal delay of these edges.

As the reference sawtooth signal is likewise generated by the FPGA, the inflection points of each incident signal, indicated by digitized edges generated by the method previously explained, could easily be compared to the corresponding inflection points of the reference signal to calculate a phase offset value for each channel. This offset will then correspond to a given error value, in that each channel will have a desired relative phase offset which the system is programmed to correct to. Phase correction is then performed in a two-step process wherein the system processor computes a compensation factor and this factor is applied to the array by means of specialized circuitry. This compensation factor is calculated by means of a 'PID' control technique which is purposed to minimize steady-state error, overshoot, and

settling time. The three letters 'PID' correspond to three computed values, namely the Proportional, Integral, and Derivative parameters, corresponding to present, past, and predicted error values, respectively. These three parameters are combined by means of a weighted sum to determine an appropriate error-correction value. A graphical representation of this process is shown below.

Figure 3.3 Phase error computation process, in which three feedback branches are summed to minimize steady-state error, overshoot, and settling time

Once calculated, the phase compensation signal is output to the phase modulator. The signal must therefore be acted on by a DAC, or digital-to-analog converter, as the modulator is naturally analog and cannot accept digital signals. This process is subsequently repeated multiple times per second for each channel in the system, constituting a closed-loop feedback system in which the proper phase correlation for each channel is constantly maintained.

The various design iterations of this system will be discussed in more detail in the following sections.

## **Chapter 4**

#### ITERATIONS OF SYSTEM DESIGN

## 4.1 4-Channel Prototype

I joined this project directly prior to the PSI Imager's Critical Design Review in May of 2010. At this point in time, EM Photonics had already begun development of the control system using the previously detailed phase control methodology. As with most circuitry projects, this particular project began on a solderless breadboard with a rough prototype of the phase detection circuitry; this prototype is shown in the following figure.

Figure 4.1 Original solderless breadboard prototype of the phase detection circuitry, indicated by the red square. The feedback distribution prototype circuitry can also be seen to the upper left of the figure.

After so proving the capacity for operational functionality, EM Photonics developed a proof-of-concept system of custom design which had the ability to synchronize the phases of four channels. This system consisted of a custom printed circuit board (PCB) and a COTS Xilinx ML-605 FPGA development board. The custom PCB contained the circuitry necessary to digitize each control channel for phase detection, and to generate the reference sawtooth signal. This PCB could be attached to an FPGA development board by means of an FMC (Field Mezzanine Connector) interface. The FPGA 'parent' board could then perform the necessary phase error calculation, determine appropriate feedback compensation, and output it back to the PCB via the same interface, and the onboard circuitry would in turn apply the feedback voltage to the modulator. The development test setup likewise incorporated two phase modulators, one for reference and the other for feedback, with which we were able to replicate the conditions of a channel working in the proposed PSI Imager, demonstrating successful closed-loop feedback control of a phase modulator.

Figure 4.2 A picture of the 4-channel prototype PCB together with a softwaregenerated 3D rendering of the same

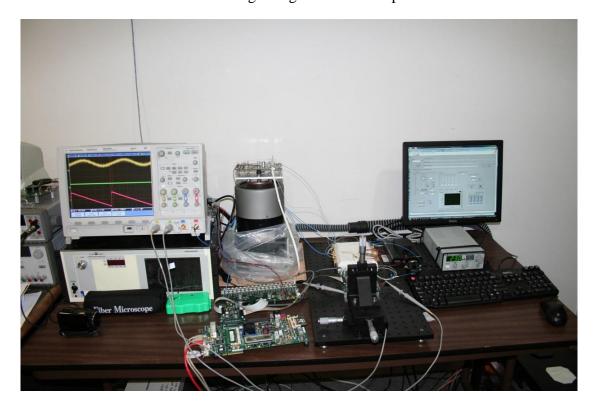

This system sampled inputs at 100kHz, or half the expected operational frequency of the subsequent iterations of the control system. Nonetheless this system was able to satisfactorily exhibit close-loop phase control of a phase-control modulator under vibration, maintaining a standard deviation of only 2.2° under no vibration and 6.8° under simulated AH-53E vibration. As this prototype was not intended for system integration, it included no electro-optic detectors for receiving optical signals. Instead, a discrete photodetector was used and its output was injected onto the PCB via test connectors.

Figure 4.3 The 4-Channel Prototype PCB mated to a Xilinx ML-605 Motherboard under test

#### 4.2 Pathfinder IIB

#### 4.2.1 Overview

PSIs first DAI imager was a thirty-channel array using 35GHz modules designated internally (and subsequently in relevant design literature) as 'Pathfinder'. The 35GHz operational frequency was chosen due to the availability of low-cost phase modulators developed for use in high-speed communication applications. This system was implemented on a standard optics table within the proper enclosures given the necessary inclusion of an IR laser.

Though known commonly to us as simply 'Pathfinder', this moniker actually describes several systems. The first, eventually known as the Pathfinder I, had been implemented with a periodic hexagonal array. The spatial periodicity of the distributed aperture, however, was found to be detrimental due to excessive aliasing and imaging artifacts. As such, PSI developed the next iteration of the system, the Pathfinder IIA, using the same RF parts as the original Pathfinder, but utilizing an aperiodic detector array in the shape of a 5-arm spiral. This new aperiodic sensor placement helped to eliminate aliases and artifacts in the images that had been seen in the previous iteration of the system. This change likewise required PSI to develop new control electronics, as the optical detectors for the phase control system had to follow the same layout as the sensors on the array face. As will soon be described in greater detail, the system designation was again changed, now the Pathfinder IIB, following the integration of our phase control electronics, the development of which is described in the following sections.

#### 4.2.2 System Topology

Following the paradigm of the four-channel prototype board, we developed a system composed of several custom PCBs and a COTS development board which provided an FPGA and several peripherals. Each RF channel assembly contained Low Noise Amplifiers (LNAs), whose power was delivered by RJ-45 connections, and phase feedback was sent over SMA, requiring two connectors to interface with each channel.

As discussed above, the 4-Channel prototype control system was implemented with the use of a Xilinx ML-605 development board. Development boards, like the one in question, are typically used in proof-of-concept or prototypical designs as they provide a considerable variety of pre-implemented interfaces and features, thereby simplifying incorporating designs (and likewise reducing associated costs). As physical space was in this instance a non-issue, we utilized the same model development board as before, replacing our original 4-channel custom PCB with an array of newly-designed custom PCBs, again designed to interface with the development board's FPGA via its mezzanine connector.

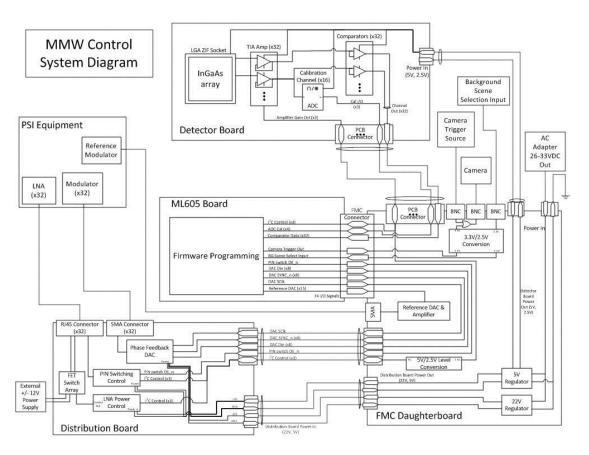

Figure 4.4 Pathfinder Electronics System Diagram.

# 4.2.3 FMC30

One of my first design tasks on this project was the FMC30 PCB. This PCB, so designated due to its connectivity to the FPGA Mezzanine Connector (FMC) and support of the 30-channel Pathfinder system, closely followed the design of the 4-Channel Prototype FMC board, but was designed for integration into the Pathfinder imaging system. Originally designated the FMC32, the PCB indeed supports 32 channels, two of which are unused as the Pathfinder does not utilize channels 10 and 29. The FMC30 is the primary interface of the FPGA processor to the rest of the system, supporting the interfaces to both peripheral boards, the Receiver30 and the

Distribution 30 PCBs, including interfaces for both communication and power. The FMC30 accepts a 26-33VDC input which mimics the AH-53 onboard power format which is then regulated so as to supply 3.3VDC and 2.5VDC to the Receiver 30 PCB and 5VDC and 22VDC to the Distribution 30 PCB. In addition to power, there is also a 51-pin flat-flex cable interface to both the Receiver 30 and Distribution 30 PCBs. These cables carried comparator outputs from the Receiver 30 PCB and phase correction voltages to the Distribution 30, as well as various communication signals such as IIC and SPI busses. The FMC 30 also holds the necessary circuitry to generate the phase reference sawtooth signal, which was output to the system's reference modulator via an SMA connector.

The FMC30 likewise handles the trigger for the SWIR camera. The board includes two ports for the trigger, one of which functions as a synchronization input as it may occasionally be desirable to trigger the camera from an external source. Support for various triggering modes was implemented in firmware, selectable from the LabVIEW GUI. A third BNC was also included to monitor the status of PIN switches in place on the Pathfinder II's phase modulators. These PIN switches essentially constituted a 'load' or background setting, which would allow the capture of noise induced by the module. While most noise is non-deterministic and can thus be mitigated by means of averaging, some noise induced by the modules is deterministic, and thus cannot be dealt with so easily. By alternating successive frames between the imaging scene and the 'load' scene, one could easily subtract the background image from the scene image, thus eliminating additive noise and improving the fidelity of the image.

Figure 4.5 The FMC30 PCB attached to its ML605 carrier

## 4.2.4 Receiver 30\_RevA and Receiver 30\_RevB

My largest responsibility in the design of the phase control electronics for the Pathfinder imaging system was the design of the Receiver PCB. While the design of the FMC30 was relatively simple and the layout was a derivative of the previous design, the Receiver board was largely new territory, posing a new challenge as a 'ground-up' design. All subsequent control systems were likewise derivatives of this design. As such, the design of the Receiver30\_RevA and the subsequent RevB will be discussed in a higher degree of detail.

#### 4.2.4.1 Optical Interface

The purpose of the Receiver board is to extract phase information from each channel and pass it to the Control board. Since the signals are carried optically, this necessitates splitting the optical signals (such that one branch can travel to the camera and the other to the Receiver board) and converting the optical signals to electrical signals with photodetectors. Since the optical channel configuration follows that of the antenna layout, these photodetectors must likewise mimic the antenna pattern. As a result of this the alignment of the Receiver board and its array of detectors is very sensitive with respect to lateral translation, magnification, and optical focus. The imaging system inside the optical processor is designed such that the short-wave infrared (SWIR) camera images the Fourier plane of the fiber array, necessitating the use of a lens to inflict the requisite far-field diffraction on the fiber array image. By contrast, the Receiver board must be placed in the image plane of the fiber array so that each channel can be individually sampled. The original Pathfinder phase control electronics developed by PSI made use of discrete photodetectors. This allows some simplification in layout, but also required magnification of the imaged fiber array for proper alignment to allow for part-clearance tolerances. This likewise necessitated the addition of more optical components which were not desired. To eliminate these additional optical components, the physical layout on the PCB must be made considerably smaller, requiring tighter design tolerances and making the use of discrete photodetectors prohibitively difficult. The solution determined was to use a focal plane array (FPA), which would be bump-bonded to a copper land pattern on the PCB surface which replicates the array layout. For a variety of reasons, detailed in the following section, we decided to modularize this portion of the design, separating the

FPA interface onto a specially-purposed Detector Interposer PCB, which would be connected to the Receiver PCB by means of a zero-insertion force (ZIF) socket.

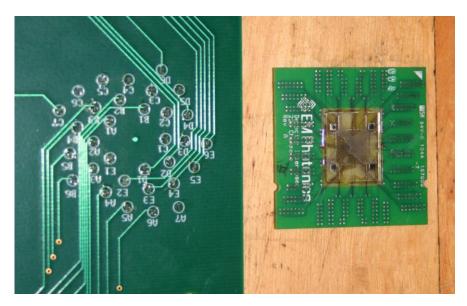

Figure 4.6 Detector Interposer PCB is shown at right, original PSI receiver layout is shown at left. The addition of the interposer removes the need for 40x optical magnification and occupies significantly less space.

# 4.2.4.2 Input Conditioning

As was discussed in the previous chapter, the input signals from the FPA are relatively weak current signals; the responsivity of the particular FPA in use was approximately 1mA of current per 1mW of optical power. As such, it is necessary to amplify each channel and perform conversion to a voltage signal before attempting to extract phase information. This circuit is shown below in Figure 4.7.

Figure 4.7 Receiver 30 Trans-impedance amplifier unit cell, showing input amplification and translation, as well as output digitization

# **4.2.4.2.1** Current Signal Translation

Op-amps are by nature differential voltage amplifiers and, as such, the input signals carried as variations in electric current must be converted to voltage signals. Within the properties of op-amp design, it is assumed that no current will pass through the inputs of an operational amplifier. The current signal can thus be effectively converted to a voltage signal by the simple relation of Ohm's law (V = IR) through a parallel resistor to ground; as no current can pass through the input of the op-amp, the effective resistance experienced by the input source is determined entirely by this value. As shown by the relation of Ohm's law, the input voltage to the op-amp is directly proportional to this resistance. A consequence of this relation is that this resistor value may be tuned to provide a desired operating range of input voltages in that the resistor value 'R' directly corresponds to resultant voltage 'V'. As such, an expected range of voltage signals will correspond directly with a given range of current signals, and so the system can be adapted to varying input levels with the substitution of only this initial resistor.

#### 4.2.4.2.2 Input Amplification

The input circuit shown in the figure above is largely the same as that used in the proof-of-concept, with a minor change. Due to a variety of parameters relating to everything from the RF modules, the optical processor, and the receiver FPA we anticipated that was likely to be a considerable amount of variance in the optical power from channel to channel, which will relate directly to the signal current from each channel. In order to support this and broaden the range of supportable input signal powers the feedback resistor of the amplifier was replaced with a potentiometer so that the gain on each channel of the system could be individually adjustable. Since such fine adjustments on so many channels would hardly be feasible by hand, our solution was to use an array of digital potentiometers with electrically-controllable wipers with a control methodology built around an I2C bus, a short explanation of which follows. The advantage of the I2C bus is that it is a well-established standard with a wide base of support in COTS devices. This method allows fine-grained user control via a terminal or GUI (graphical user interface), but also lends itself easily to automation in that it can be independently controlled by the processor without requiring interaction from the user.

#### 4.2.4.3 I2C Bus Operation

The I2C standard denotes a single-ended (or non-differential) serial communication interface consisting of a clock signal, designated SCL, and a data signal, designated SDA. A third signal, an active-negative reset is often employed and was included in our design, but is not strictly necessary. A serial bus, such as this, meets our needs here perfectly as the gain control for the amplifiers need not be high speed, and the serial nature of the bus requiring only two conductors adds minimal

complication to the design. The communication on the bus takes place under the assumption that one device is acting as the 'master', the FPGA in our case, broadcasting messages to the rest of the devices on the bus, which act as 'slaves'. Some bus topologies include multiple masters, but it remains true in such cases that only one master can use the bus at a time. Generally, the communication follows the standard that the master will send out the specific address of the slave chip it wishes to address with an additional bit denoting its intention to 'read' or to 'write', meaning to ascertain the current state of the slave device or to overwrite its current state with new data, which will be met with an acknowledge from the device if connected. In the case of a write, the master will then transmit the memory address of the specific register it wishes to write (generally the address of the wiper value to set in our case) followed by the data to be stored there, each again met with an acknowledge from the targeted device. Otherwise, in the event of a read, the slave will respond with the contents of whatever register was last accessed, thus a read operation generally begins with a write command to the desired register, but without actually overwriting the data contained therein. In either case, assuming the transaction is successful on all points, the device will acknowledge again and the exchange is complete.

#### 4.2.4.4 Bus Multiplexing

Another complication added to our gain control methodology was bus multiplexing. As implied above, devices on the bus are differentiated by means of addressing; in general, a chip operating on an I2C bus has an address which is mostly hard-wired with the last bits determined by physical input pins. As devices of the same model have the same hard-wired address component, the number of devices that can be used on a single bus is determined by how many unique addresses can be made

with the physical address pins. In the case of the digital potentiometers we specified for this design, there were two pins meaning that only four devices of the same model could exist on the same bus, addressed '00', '01', '10', and '11', respectively. In order to support all the digital potentiometers required in the design it was necessary to multiplex multiple busses with an I2C switch, each individual bus then supporting four uniquely-addressed potentiometers. This adds a prerequisite step to the bus communication, in that the switch must be addressed first and told which bus is needed before communication can be passed through. Though an added complication, we were able to abstract this in software such that merely indicating a channel index would automatically address the appropriate bus as part of the routine.

This bus multiplexing also achieved a secondary purpose in the way of automatic level conversion. An I2C is connected to a particular source voltage by means of pull-up resistors, such that it need only be driven 'low' to transmit data. As such, an I2C bus in a resting state is always sitting 'high', where it remains until the master device pulls it low. The FPGA we employed included ports specifically purposed to drive I2C buses at 2.5V, but the digital potentiometers we specified were designed to receive control messages on a 3.3V bus. This brings into account a principle known as 'hysteresis', or the necessary conditions for a digital device to recognize a change in state from 'high' to 'low' or vice-versa. In general, hysteresis requirements dictate the specific percentage of VCC that a signal must achieve to constitute a rising edge condition and the corresponding percentage it must drop below to constitute a falling edge condition. This concept is important because it allows for a certain level of fluctuation or noise on a digital signal without recognizing this as a change of state, however it also means that a 2.5V digital signal cannot be used to

control a 3.3V digital signal if the 'high' requirement is greater than  $\sim$ 75% (2.5/3.3), thus necessitating the use of an intermediary level-conversion circuit.

# 4.2.4.5 Receiver 30\_RevB Upgrades

After test and verification of the Receiver30\_RevA PCB, we identified additional needs and began to formulate a series of upgrades that would be beneficial to integration with the Pathfinder imaging system.

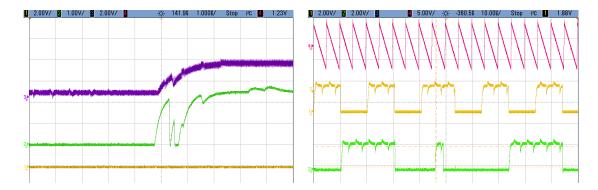

Of particular concern was optical alignment; we had expected this process to be difficult, and found isolation of individual channels to be problematic during testing. As such, we devised a system to alleviate this. Five additional channels were added to the fiber array to assist in the alignment process, these located in each of the four corners of the array and at its center. These channels were fed directly from a laser, and were not subjected to phase modulation. A new block of input-conditioning amplifiers was introduced in the PCB layout, but with no comparators as there was no need for phase extraction. The amplifier outputs, essentially just DC input as no modulation was present, were then fed individually to 8-bit ADC (analog-to-digital converters), the eight bits of which were fed to eight LEDs. As such, during the alignment procedure, the eight LEDs pertaining to any of the four alignment channels would show an 8-bit binary representation of input power, the intent being to provide visual feedback such that the board could be effectively aligned by moving the board until all four channels were maximized. These modifications to the Receiver design are shown below in Figure 4.8.

Figure 4.8 A comparison of the layouts of the Receiver30\_RevA (left) and Receiver30\_RevB. The addition of alignment LEDs and the necessary driving circuitry is showing surrounding the Detector Interposer socket. Additional ADC channels are also present.

This iteration of the Receiver board also saw some changes to the input circuit topology with the addition of a series filtering capacitor placed at each signal input to set the channel bandwidth. Together with the pre-existing parallel resistor to ground, this circuit now comprises a classic low-pass filter with a cutoff determined by the following relation:

$$Fc = \frac{1}{2\pi RC}$$

This is necessary as the gain-bandwidth-product of the operational amplifier may allow for some high-frequency noise to be amplified along with the signal. This value was set such that there would be no distortion imposed on the input signals, but that the high-frequency noise would be attenuated.

Figure 4.9 Modifications to the input circuitry of the Receiver board include the addition of a low-pass filter

The final major modification to the design was the inclusion of 16 more ADC sampling channels. This was necessary, in part, to support the addition of the alignment channels, but was also beneficial for system operation in general. The RevA design had included amplitude sampling support for only half of the input channels, but we found this feature particularly useful in testing and opted to expand it to the remaining channels. As each ADC sampling IC can support 16 inputs, the RevB design can support 32 channels in this manner. The addition of the four alignment channels necessitated that two of the thirty operational channels would not be sampled, but this was deemed an appropriate risk.

Schematic design and circuit board layout were accomplished with software using National Instruments Circuit Design Suite.

#### 4.2.5 Detector Interposer

Figure 4.10 Conceptual rendering of the Detector Interposer PCB and its interfaces